## Asynchronous Circuit Design

Chris J. Myers

Lecture 6: Muller Circuits Chapter 6

#### **Muller Circuits**

- Uses the unbounded gate delay model.

- Circuits are guaranteed to work regardless of gate delays assuming that wire delays are negligible.

- Requires knowledge of the allowed behaviors of the environment.

- There are no restrictions on the speed of the environment.

#### Muller Circuit Design

- Translate higher level specification into a *state graph*.

- If not *complete state coded*, change the protocol or add new internal state signal(s).

- Derive logic using modified logic minimization procedure.

- Map design to gates in a given gate library.

#### Overview

- Formal definition of speed independence.

- State assignment of Muller circuits.

- Logic minimization of Muller circuits.

- Technology mapping of Muller circuits.

#### **Complete Circuits**

- To design a speed independent circuit, must have complete information about both the circuit and its environment.

- We restrict our attention to complete circuits.

- A complete circuit C is defined by a finite set of states, S.

- At any time, *C* is said to be in one of these states.

#### **Allowed Sequences**

- Behavior of a complete circuit is defined by set of allowed sequences of states.

- Each allowed sequence can be either finite or infinite, and the set of allowed sequences can also be finite or infinite.

- The sequence ( $s_1, s_2, s_3, ...$ ) says that state  $s_1$  is followed by state  $s_2$ , but it does not state at what time.

#### **Properties of Allowed Sequences**

- For a sequence ( $s_1, s_2, ...$ ), consecutive states must be different (i.e.,  $s_i \neq s_{i+1}$ ).

- Each state  $s \in S$  is the initial state of some allowed sequence.

- If  $(s_1, s_2, s_3, ...)$  is allowed sequence then so is  $(s_2, s_3, ...)$ .

- If  $(s_1, s_2, ...)$  and  $(t_1, t_2, ...)$  are allowed sequences and  $s_2 = t_1$ , then  $(s_1, t_1, t_2, ...)$  is also an allowed sequence.

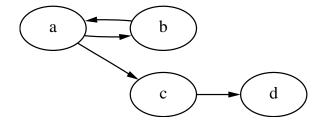

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, ...

- a, c, d

- The sequences above imply the following allowed sequences:

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, ...

- a, c, d

- The sequences above imply the following allowed sequences:

- **●** b, a, b, a, . . .

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, ...

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- **●** a, b, a, b, . . .

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- 6 d

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, . . .

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- d

- $\bigcirc$  a, b, a, c, d

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, . . .

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- d

- a, b, a, c, d

- a, b, a, b, a, c, d

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, . . .

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- **3** d

- a, b, a, c, d

- a, b, a, b, a, c, d

- b, a, c, d

- Consider a complete circuit composed of four states,  $S = \{a, b, c, d\}$ , which has the following two allowed sequences:

- a, b, a, b, ...

- a, c, d

- The sequences above imply the following allowed sequences:

- b, a, b, a, . . .

- 2 c, d

- 6 d

- a, b, a, c, d

- a, b, a, b, a, c, d

- b, a, c, d

- etc.

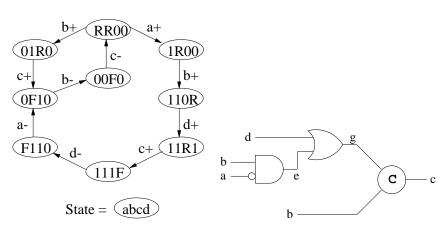

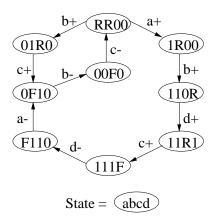

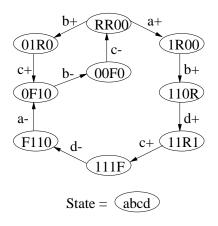

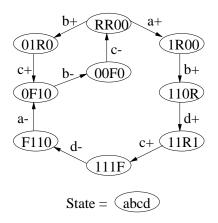

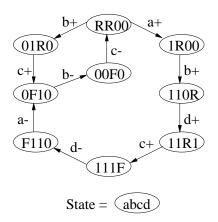

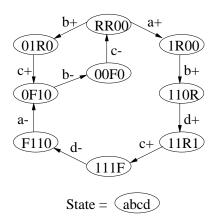

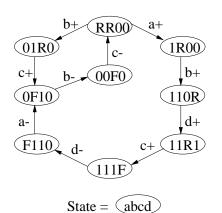

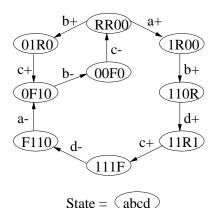

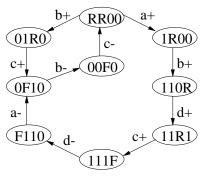

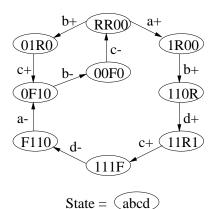

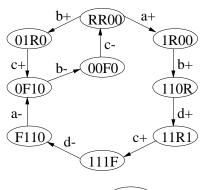

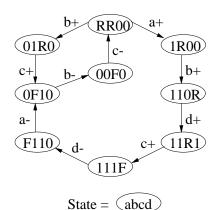

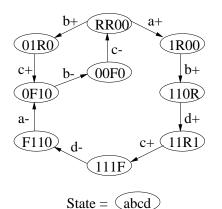

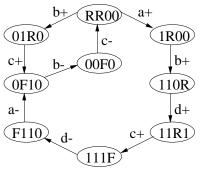

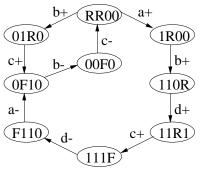

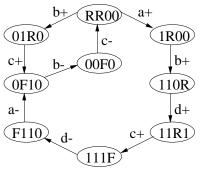

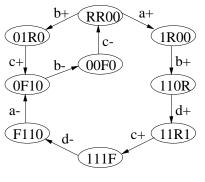

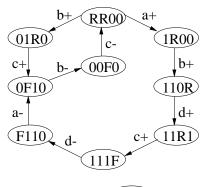

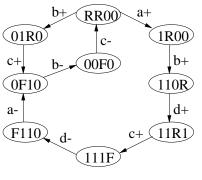

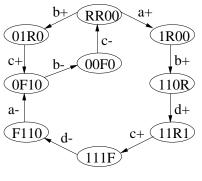

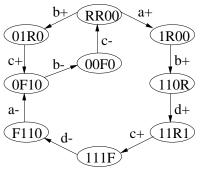

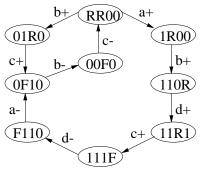

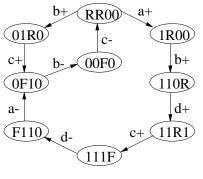

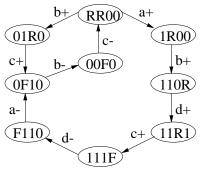

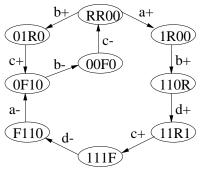

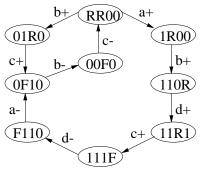

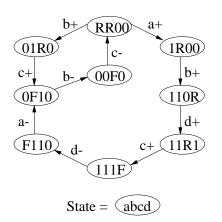

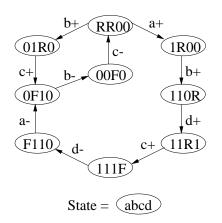

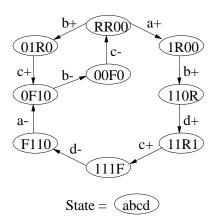

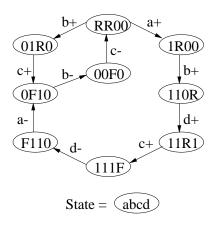

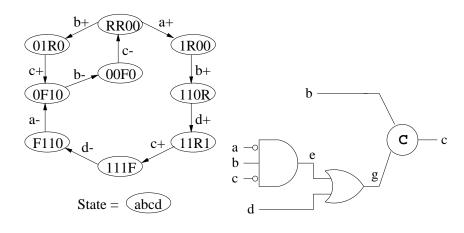

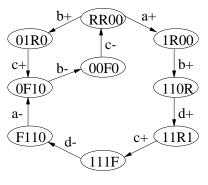

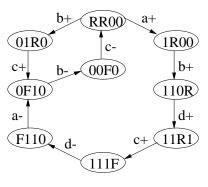

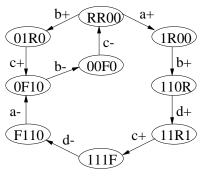

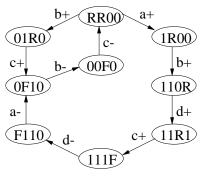

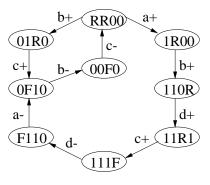

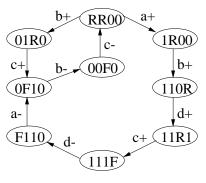

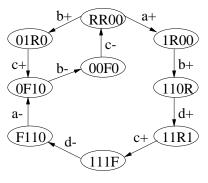

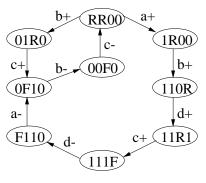

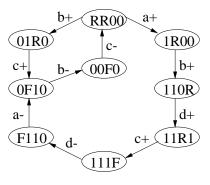

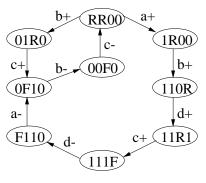

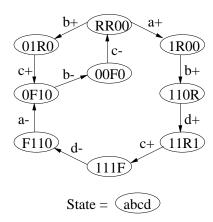

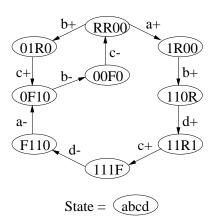

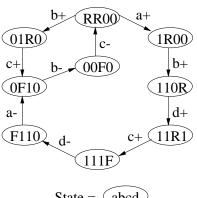

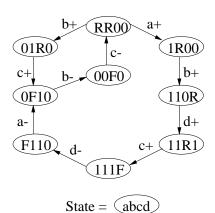

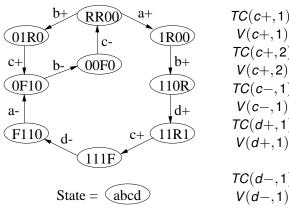

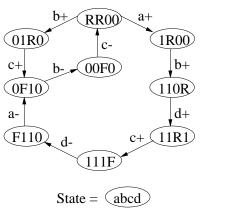

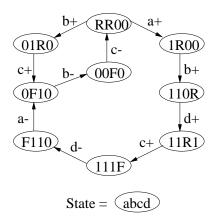

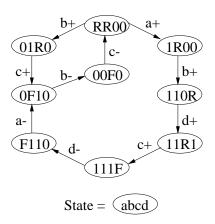

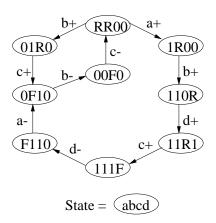

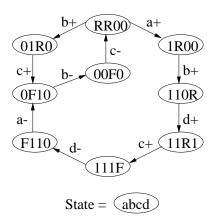

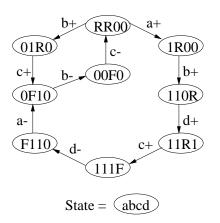

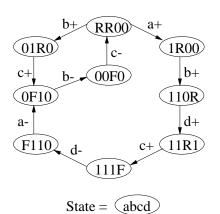

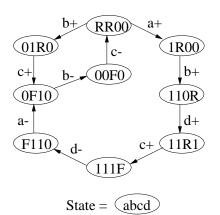

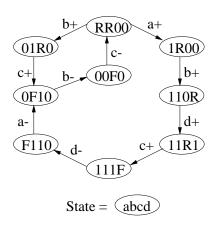

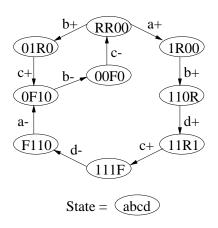

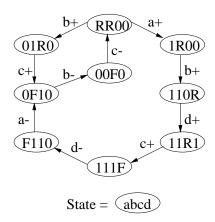

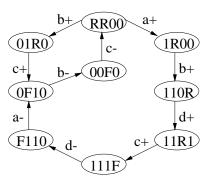

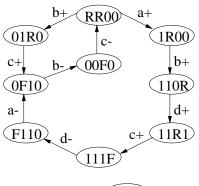

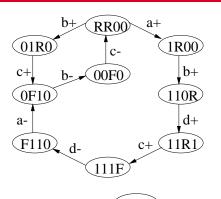

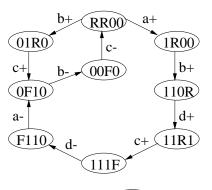

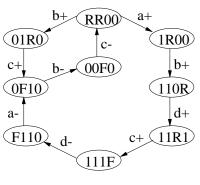

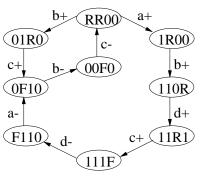

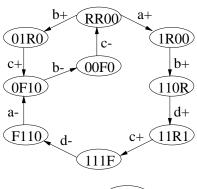

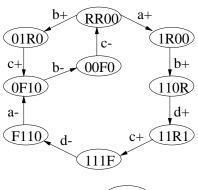

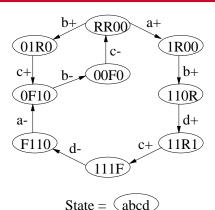

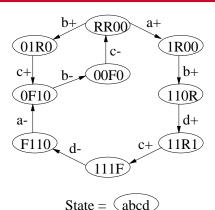

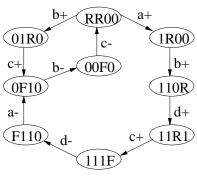

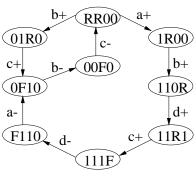

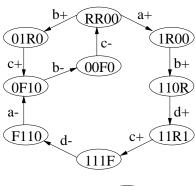

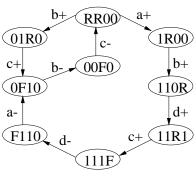

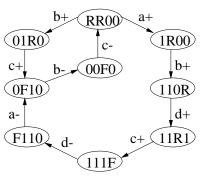

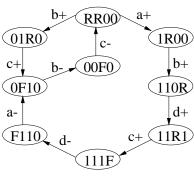

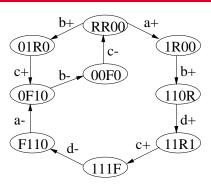

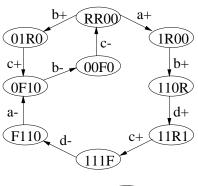

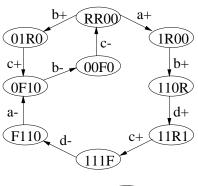

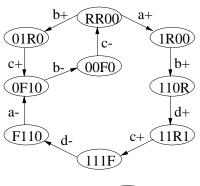

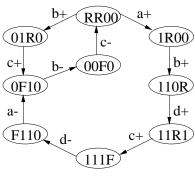

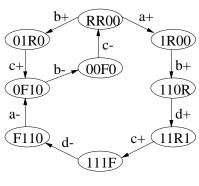

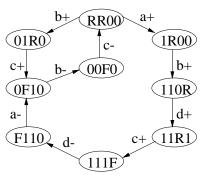

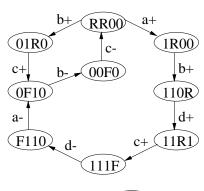

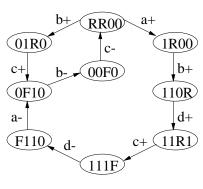

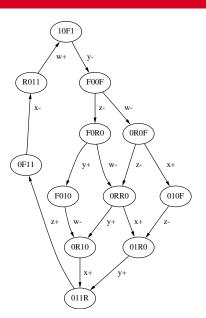

# State Diagram For Simple Example

# $\mathcal{R}$ -related and $\mathcal{R}$ -sequences

- Two states  $s_i, s_j \in S$  are  $\mathcal{R}$ -related, (denoted  $s_i \mathcal{R} s_j$ ) when:

- $\mathbf{0}$   $s_i = s_i$  or

- A sequence (  $s_1, s_2, ..., s_m$  ) is an  $\mathcal{R}$ -sequence if  $s_i \mathcal{R} s_{i+1}$  for each 1 < i < m-1.

#### The Followed and Equivalence Relations

- A state  $s_i$  is *followed* by a state  $s_j$  (denoted  $s_i \mathcal{F} s_j$ ) if there exists an  $\mathcal{R}$ -sequence ( $s_i, \ldots, s_i$ ).

- ullet The  ${\mathcal F}$ -relation is reflexive and transitive, but not necessarily symmetric.

- If two states  $s_i$  and  $s_j$  are symmetric under the  $\mathcal{F}$ -relation (i.e.,  $s_i \mathcal{F} s_j$  and  $s_i \mathcal{F} s_i$ ), they are said to be *equivalent* (denoted  $s_i \mathcal{E} s_i$ ).

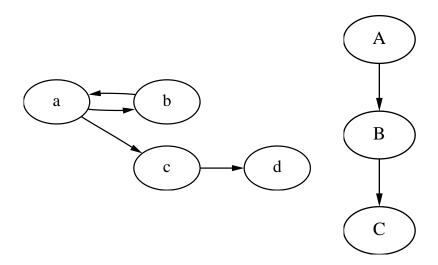

#### **Equivalence Classes**

- The equivalence relation  $\mathcal{E}$  partitions the finite set of states S of any circuit into equivalence classes of states.

- The  $\mathcal{F}$ -relation can be extended to these equivalence classes.

- If A and B are two equivalence classes, then  $A\mathcal{F}B$  if there exists states  $a \in A$  and  $b \in B$  such that  $a\mathcal{F}b$ .

- If  $a \in A$  and  $b \in B$  and  $A \mathcal{F} B$ , then  $a \mathcal{F} b$ .

#### Speed Independence

- For any allowed sequence, there is a definite last class which is called the terminal class.

- A circuit *C* is *speed independent with respect to a state s* if all allowed sequences starting with *s* have the same terminal class.

# Equivalence Classes for Simple Example

## Allowed Sequences on State Graphs

- An allowed sequence of states (s<sub>1</sub>, s<sub>2</sub>, ...) is any sequence of states satisfying the following three conditions:

- **1** No two consecutive states  $s_i$  and  $s_{i+1}$  are equal.

- 2 For any state  $s_{i+1}$  and signal  $u_i$  one of the following is true:

$$s_{j+1}(i) = s_j(i)$$

$s_{j+1}(i) = s'_i(i)$

If there exists a signal  $u_i$  and a state  $s_j$  such that  $s_j(i) = s_r(i)$  and  $s'_i(i) = s'_r(i)$  for all  $s_r$  in the sequence following  $s_i$ , then

$$s_j(i) = s'_j(i)$$

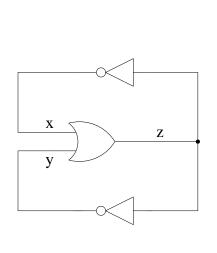

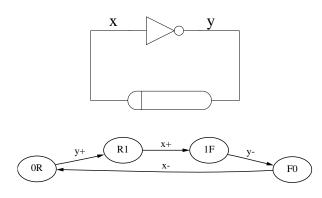

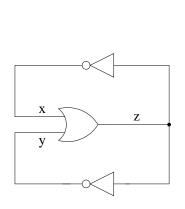

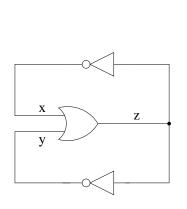

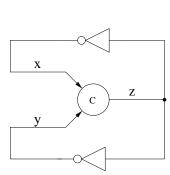

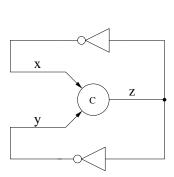

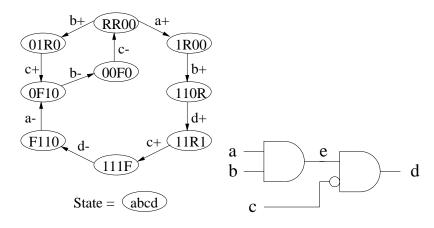

# Simple Speed-Independent Circuit

## **Totally Sequential**

• A circuit is *totally sequential* with respect to a state *s* if there is only one allowed sequence starting with *s*.

# Semi-Modularity

A circuit is semi-modular if in each state in which multiple signals are

excited, that in the states reached after one signal has transitioned, that

the remaining signals are still excited.

$$\forall t_1, t_2 \in \mathcal{T} : (s_i, t_1, s_j) \in \delta \land (s_i, t_2, s_k) \in \delta$$

$$\Rightarrow \exists s_l \in \mathcal{S} : (s_j, t_2, s_l) \in \delta \land (s_k, t_1, s_l) \in \delta$$

- A totally sequential circuit is semi-modular but the converse is not necessarily true.

- A semi-modular circuit is also speed independent, but again the converse is not necessarily true.

### A Non-Semi-Modular Example

# A Simple Semi-Modular Speed Independent Circuit

# Output Semi-Modularity

- Input transitions are typically allowed to be disabled by other input transitions, so another useful class of circuits are those which are output semi-modular.

- A SG is output semi-modular if only input signal transitions can disable other input signal transitions.

$$\begin{aligned} \forall \mathit{t}_1 \in \mathit{T}_{\mathit{O}} \ . \ \forall \mathit{t}_2 \in \mathit{T} \ . \ (\mathit{s}_i, \mathit{t}_1, \mathit{s}_j) \in \delta \land (\mathit{s}_i, \mathit{t}_2, \mathit{s}_k) \in \delta \\ \Rightarrow \ \exists \mathit{s}_l \in \mathit{S} \ . \ (\mathit{s}_j, \mathit{t}_2, \mathit{s}_l) \in \delta \land (\mathit{s}_k, \mathit{t}_1, \mathit{s}_l) \in \delta \end{aligned}$$

where  $T_O$  is the set of output transitions (i.e.,  $T_O = \{u+, u- \mid u \in O\}$ ).

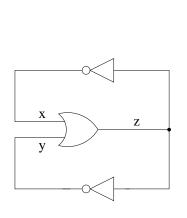

# Output Semi-Modularity Example

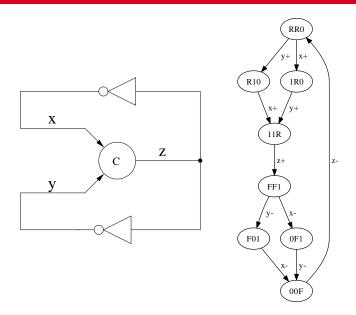

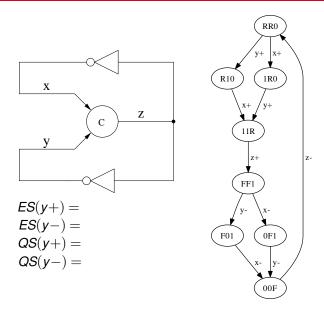

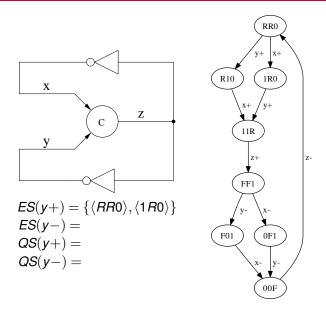

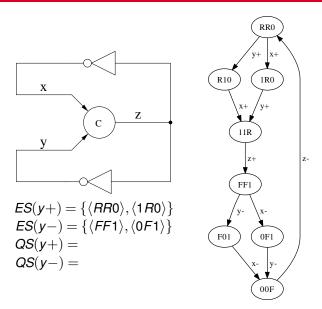

#### **Excitation States**

- It is often useful to be able to determine in which states a signal is excited to rise or fall.

- The sets of excitation states, ES(u+) and ES(u-), are defined as follows:

$$ES(u+) = \{s \in S \mid s(u) = 0 \land u \in X(s)\}$$

$$ES(u-) = \{s \in S \mid s(u) = 1 \land u \in X(s)\}$$

• Recall that X(s) is the set of signals that are excited in state s.

#### **Quiescent States**

- For each signal u, there are two sets of *quiescent states*.

- The sets QS(u+) and QS(u-) are defined as follows:

$$QS(u+) = \{ s \in S \mid s(u) = 1 \land u \notin X(s) \}$$

$$QS(u-) = \{ s \in S \mid s(u) = 0 \land u \notin X(s) \}$$

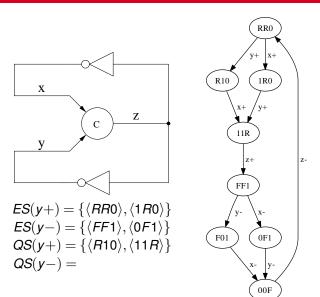

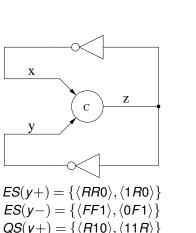

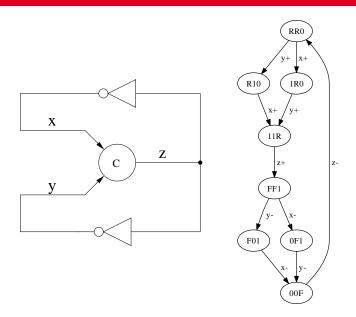

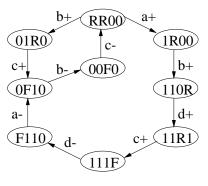

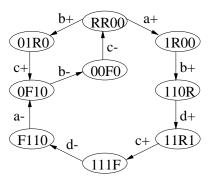

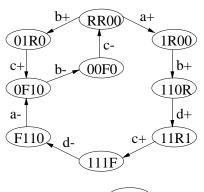

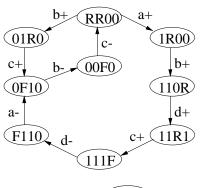

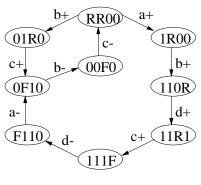

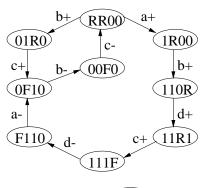

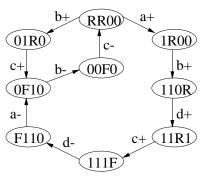

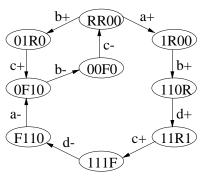

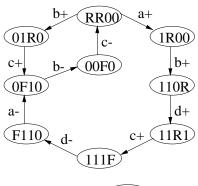

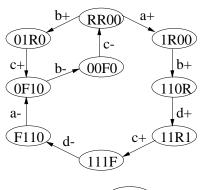

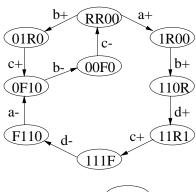

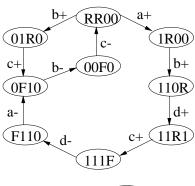

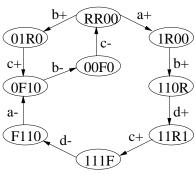

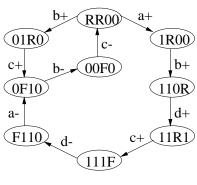

$$ES(y+) = \{\langle RHO \rangle, \langle 1HO \rangle\}$$

$$ES(y-) = \{\langle FF1 \rangle, \langle 0F1 \rangle\}$$

$$QS(y+) = \{\langle R10 \rangle, \langle 11R \rangle\}$$

$$QS(y-) = \{\langle F01 \rangle, \langle 00F \rangle\}$$

### **Excitation Regions**

- An excitation region for signal u is a maximally connected subset of either ES(u+) or ES(u-).

- If it is a subset of ES(u+), it is a set region (denoted ER(u+,k)).

- Similarly, a *reset region* is denoted ER(u-,k).

# **Switching Regions**

The switching region for a transition u\*, SR(u\*,k), is the set of states directly reachable through transition u\*:

$$SR(u*,k) = \{s_i \in S \mid \exists s_i \in ER(u*,k).(s_i,u*,s_i) \in \delta\}$$

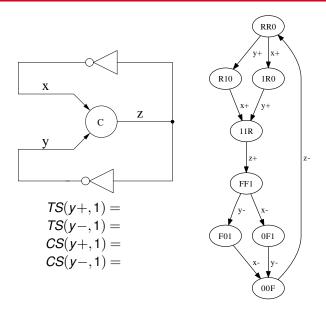

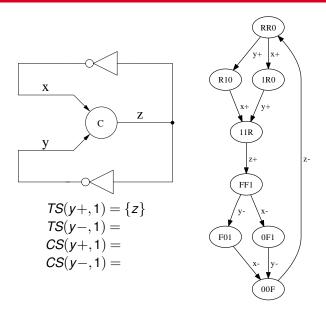

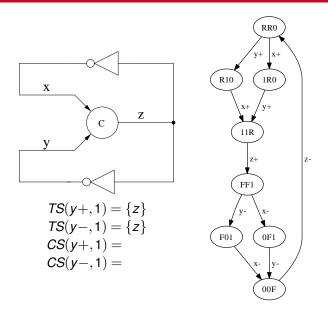

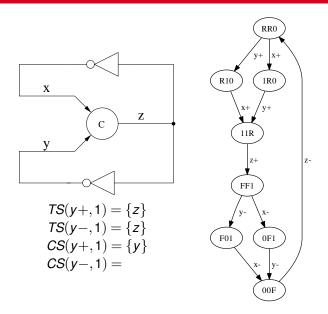

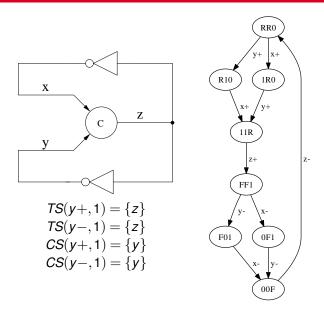

$$ER(y+,1) = ER(y-,1) = SR(y+,1) = SR(y-,1) =$$

$$ER(y+,1) = \{\langle RR0 \rangle, \langle 1R0 \rangle\}$$

$ER(y-,1) =$

$SR(y+,1) =$

$SR(y-,1) =$

$$ER(y+,1) = \{\langle RR0 \rangle, \langle 1R0 \rangle\}$$

$$ER(y-,1) = \{\langle FF1 \rangle, \langle 0F1 \rangle\}$$

$$SR(y+,1) =$$

$$SR(y-,1) =$$

$$\begin{split} &ER(y+,1) = \{\langle RR0 \rangle, \langle 1R0 \rangle\} \\ &ER(y-,1) = \{\langle FF1 \rangle, \langle 0F1 \rangle\} \\ &SR(y+,1) = \{\langle R10 \rangle, \langle 11R \rangle\} \\ &SR(y-,1) = \end{split}$$

$$\begin{split} ER(y+,1) &= \{\langle RR0\rangle, \langle 1R0\rangle\} \\ ER(y-,1) &= \{\langle FF1\rangle, \langle 0F1\rangle\} \\ SR(y+,1) &= \{\langle R10\rangle, \langle 11R\rangle\} \\ SR(y-,1) &= \{\langle F01\rangle, \langle 00F\rangle\} \end{split}$$

#### Distributive State Graphs

- A state graph is distributive if each excitation region has a unique minimal state.

- A minimal state for ER(u\*,k) is a state in ER(u\*,k) which cannot be directly reached by any other state in ER(u\*,k).

- More formally, a SG is distributive if:

$$orall extbf{\textit{ER}}(u*,k)$$

.  $\exists extbf{exactly one } s_j \in extbf{\textit{ER}}(u*,k)$  .  $\neg \exists s_i \in extbf{\textit{ER}}(u*,k)$  .  $(s_i,t,s_i) \in \delta$

# A Distributive State Graph

# A Non-Distributive State Graph

### Trigger Signals

- Each cube in the implementation is composed of trigger signals and context signals.

- For an excitation region, a trigger signal is a signal whose firing can cause the circuit to enter the excitation region.

- The set of trigger signals for an excitation region ER(u\*,k) is:

$$TS(u*,k) = \{ v \in N \mid \exists s_i, s_j \in S.((s_i, t, s_j) \in \delta) \\ \land (t = v + \lor t = v -) \\ \land (s_i \notin ER(u*,k)) \land (s_j \in ER(u*,k)) \}$$

#### Context Signals

- Any non-trigger signal which is stable in the excitation region can potentially be a context signal.

- The set of context signals for an excitation region ER(u\*,k) is:

$$CS(u*,k) = \{v_i \in N \mid v_i \notin TS(u*,k) \\ \wedge \forall s_j, s_l \in ER(u*,k).s_j(i) = s_l(i)\}$$

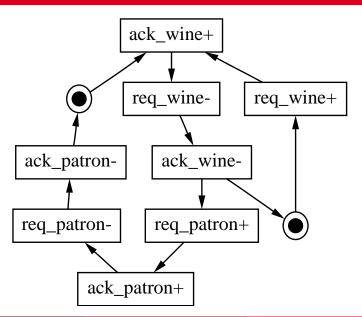

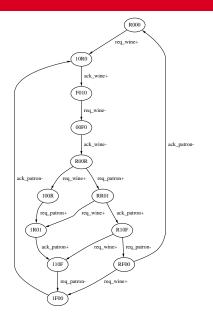

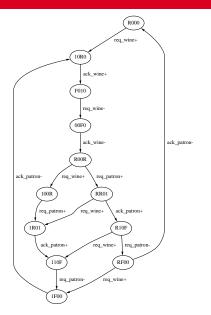

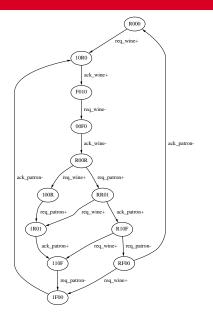

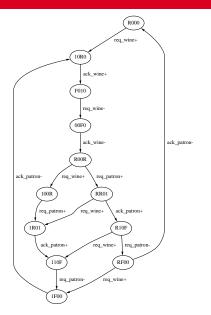

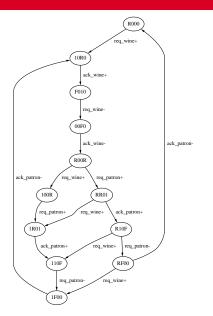

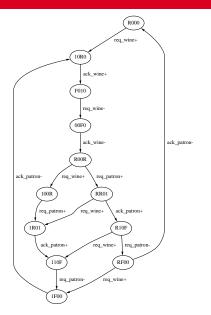

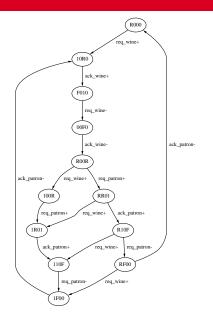

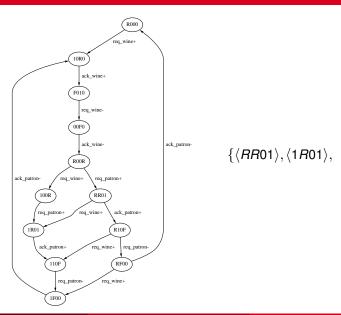

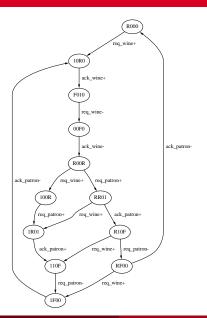

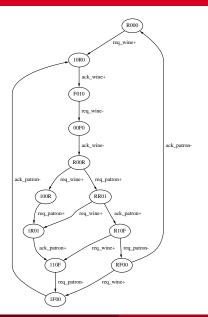

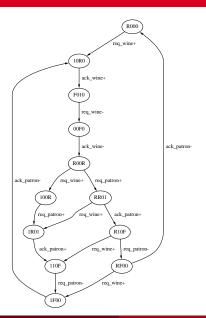

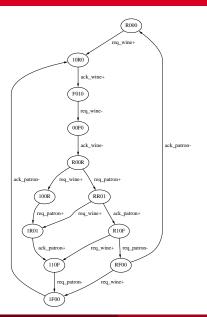

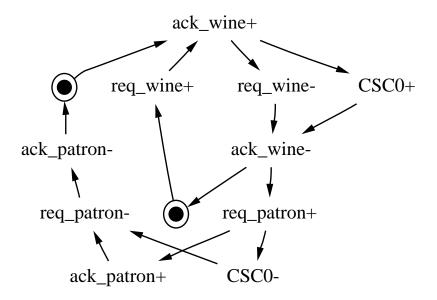

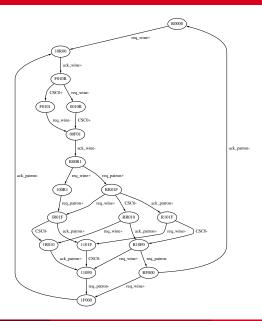

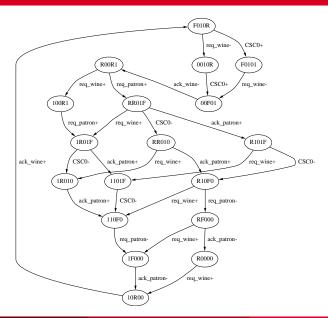

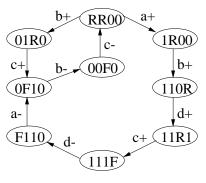

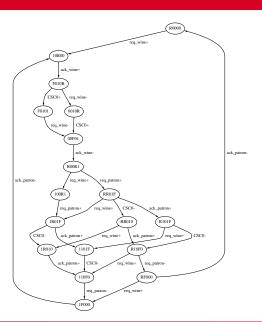

# The Passive/Active Wine Shop: Petri-net

```

ES(req_patron+) =

ES(req_patron-) =

QS(req_patron+) =

QS(req_patron-) =

```

```

\begin{split} ER(req\_patron+,1) &= \\ ER(req\_patron-,1) &= \\ SR(req\_patron+,1) &= \\ SR(req\_patron-,1) &= \\ TS(req\_patron+,1) &= \\ TS(req\_patron-,1) &= \\ CS(req\_patron+,1) &= \\ \end{split}

```

CS(reg patron-,1) =

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg patron-) =

QS(req patron+) =

QS(req_patron-) =

ER(reg\ patron+,1) =

ER(reg\ patron-,1) =

SR(req\_patron+,1) =

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(reg\ patron-,1) =

CS(reg patron+,1) =

```

CS(reg patron-,1) =

```

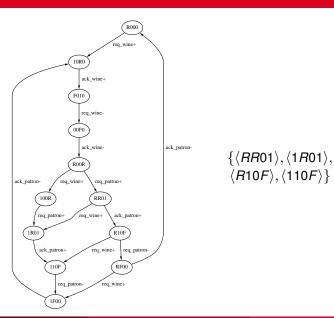

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(req patron+) =

QS(req_patron-) =

ER(reg\ patron+,1) =

ER(reg\ patron-,1) =

SR(reg\ patron+,1) =

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(req patron-,1) =

```

$$CS(req\_patron-, 1) =$$

CS(reg patron+,1) =

```

\begin{split} &\textit{ES}(\textit{req\_patron}+) = \{\langle \textit{R00R} \rangle, \langle \textit{100R} \rangle\} \\ &\textit{ES}(\textit{req\_patron}-) = \{\langle \textit{R10F} \rangle, \langle \textit{110F} \rangle\} \\ &\textit{QS}(\textit{req\_patron}+) = \{\langle \textit{RR01} \rangle, \langle \textit{1R01} \rangle\} \\ &\textit{QS}(\textit{req\_patron}-) = \end{split}

```

```

\begin{split} ER(\textit{req\_patron}+,1) &= \\ ER(\textit{req\_patron}-,1) &= \\ SR(\textit{req\_patron}+,1) &= \\ SR(\textit{req\_patron}-,1) &= \\ TS(\textit{req\_patron}+,1) &= \\ TS(\textit{req\_patron}-,1) &= \\ CS(\textit{req\_patron}+,1) &= \\ CS(\textit{req\_patron}-,1) &= \\ CS(\textit{req\_patro

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) =

ER(reg\ patron-,1) =

SR(reg\ patron+,1) =

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(req patron-,1) =

CS(req patron+, 1) =

CS(\text{reg patron}-,1) =

```

```

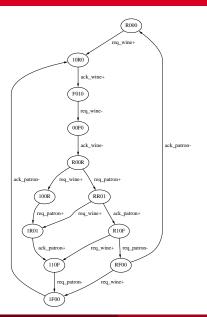

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(reg\ patron-,1) =

SR(reg\ patron+,1) =

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(req patron-,1) =

CS(req patron+, 1) =

CS(\text{reg patron}-,1) =

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) =

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(req patron-,1) =

CS(req patron+, 1) =

```

CS(reg patron-,1) =

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(req\_patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(reg\ patron-,1) =

TS(reg\ patron+,1) =

TS(req patron-,1) =

CS(req patron+, 1) =

```

```

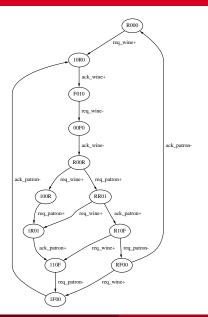

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(req\_patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(req\_patron-,1) = \{\langle RF00 \rangle, \langle 1F00 \rangle\}

TS(req\_patron+,1) =

TS(req patron-,1) =

CS(req patron+, 1) =

CS(\text{reg patron}-,1) =

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(reg\ patron-,1) = \{\langle RF00\rangle, \langle 1F00\rangle\}

TS(reg patron+,1) = \{ack wine\}

TS(req patron-,1) =

CS(req patron+, 1) =

CS(\text{reg patron}-,1) =

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(reg\ patron-,1) = \{\langle RF00\rangle, \langle 1F00\rangle\}

TS(reg patron+,1) = \{ack wine\}

TS(req patron-,1) = \{ack patron\}

CS(reg patron+,1) =

CS(\text{reg patron}-,1) =

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(reg\ patron-,1) = \{\langle RF00\rangle, \langle 1F00\rangle\}

TS(reg\ patron+,1) = \{ack\ wine\}

TS(reg\ patron-,1) = \{ack\ patron\}

CS(reg patron+,1) = \{ack patron,

req patron}

CS(\text{req patron}-,1) =

```

```

ES(reg\ patron+) = \{\langle R00R \rangle, \langle 100R \rangle\}

ES(reg\ patron-) = \{\langle R10F \rangle, \langle 110F \rangle\}

QS(reg\ patron+) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

QS(reg\ patron-) = \{\langle RF00 \rangle, \langle 1F00 \rangle, \langle 1F

\langle R000\rangle, \langle 10R0\rangle,

\langle F010 \rangle, \langle 00F0 \rangle \}

ER(reg\ patron+,1) = \{\langle R00R \rangle, \langle 100R \rangle\}

ER(req\_patron-,1) = \{\langle R10F \rangle, \langle 110F \rangle\}

SR(reg\ patron+,1) = \{\langle RR01 \rangle, \langle 1R01 \rangle\}

SR(reg\ patron-,1) = \{\langle RF00\rangle, \langle 1F00\rangle\}

TS(reg\ patron+,1) = \{ack\ wine\}

TS(reg\ patron-,1) = \{ack\ patron\}

CS(reg patron+,1) = \{ack patron,

req patron}

CS(\text{req patron}-,1) = \{ack \text{ wine, }

req patron}

```

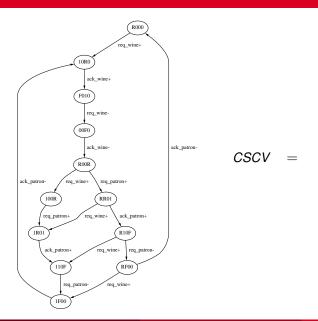

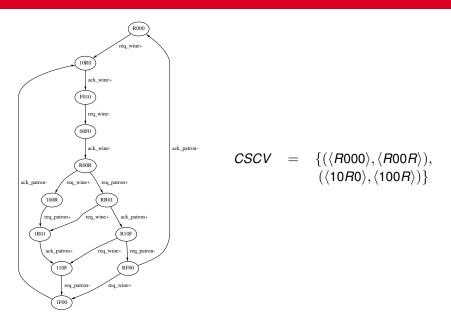

### Unique State Codes (USC)

Two states have unique state codes (USC) if they are labeled with different binary vectors.

$$USC(s_i, s_j) \Leftrightarrow \lambda_{\mathcal{S}}(s_i) \neq \lambda_{\mathcal{S}}(s_j)$$

A SG has USC if all states pairs have USC.

$$\mathit{USC}(S) \Leftrightarrow \forall (s_i, s_j) \in \mathit{S} \times \mathit{S} . \, \mathit{USC}(s_i, s_j)$$

### Complete State Codes (CSC)

Two states have complete state codes (CSC) if they either have USC or if they do not have USC but do have the same output signals excited in each state.

$$CSC(s_i, s_j) \Leftrightarrow USC(s_i, s_j) \lor X(s_i) \cap O = X(s_j) \cap O$$

$$CSC(S) \Leftrightarrow \forall (s_i, s_j) \in S \times S . CSC(s_i, s_j)$$

A set of state pairs which violate CSC is defined as:

$$CSCV(S) = \{(s_i, s_j) \in S \times S \mid \neg CSC(s_i, s_j)\}$$

#### The CSC Problem

- If a circuit does not have USC but has CSC, then the present state/next state relationship is not unique for input signals.

- Circuit only synthesized for outputs, so not a problem.

- When a circuit does not have CSC, the present state/next state relationship for output signals is ambiguous.

- Could reshuffle the protocol as described earlier.

- Now introduce method for inserting state variables.

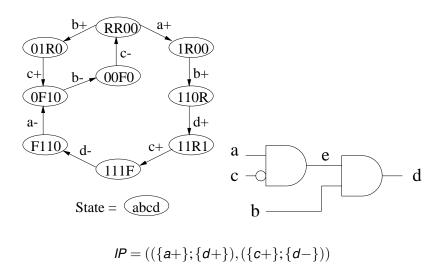

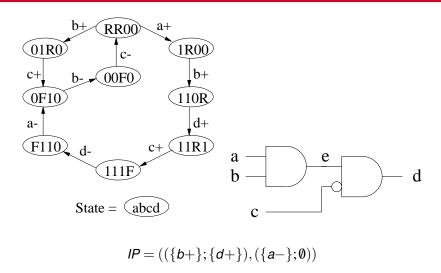

#### **Insertion Points**

- Need to insert a rising and falling transition for new signal.

- A transition point is  $TP = (t_s, t_e)$ , where  $t_s$  is a set of *start transitions* and  $t_e$  is a set of *end transitions*.

- The transition point represents the location in the protocol in which a transition on a new state signal is to be inserted.

- In a Petri net, a TP represents a transition with incoming arcs from  $t_s$  and with outgoing arcs to  $t_e$ .

- An *insertion point* is  $IP = (TP_R, TP_F)$ , where  $TP_R$  is for the rising transition and  $TP_F$  is for the falling transition.

#### **Transitioning States**

- It is necessary to determine in which states a transition can occur when inserted into a TP.

- The transtion on the new state signal becomes excited when the circuit enters  $\cap_{t \in t_s} SR(t)$ .

- Once this transition becomes excited it may remain excited in any subsequent states until there is a transition in t<sub>e</sub>.

- The set of states in which a new transition is excited is defined recursively as follows:

$$\begin{array}{lcl} \mathcal{S}(\mathit{TP}) & = & \{s_j \in \mathcal{S} \mid s_j \in \cap_{t \in t_s} \mathit{SR}(t) \lor \\ & & (\exists (s_i, t, s_j) \in \delta \ . \ s_i \in \mathit{S}(\mathit{TP}) \land t \not \in t_e)\} \end{array}$$

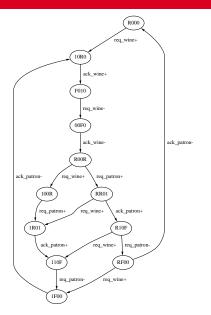

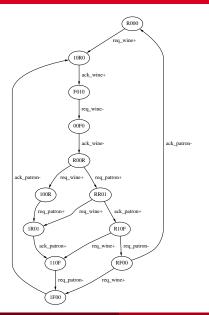

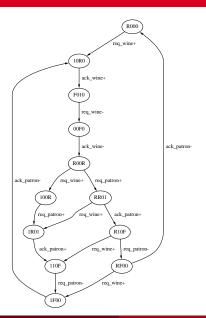

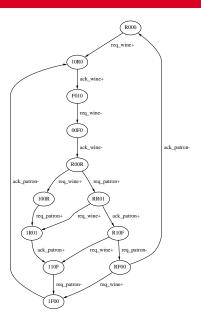

# $TP = (\{req\_patron + \}, \{req\_patron - \})$

### $TP = (\{req\_patron+\}, \{req\_patron-\})$

## $TP = (\{req\_patron+\}, \{req\_patron-\})$

#### Insertion Point Explosion

- The set of all possible insertion points includes all combinations of transitions in t<sub>s</sub> and t<sub>e</sub> for TP<sub>R</sub> and TP<sub>F</sub>.

- Upper bound on number of possible insertion points is  $2^{|T|^4}$ .

- Fortunately, many of these insertion points can be quickly eliminated because they either:

- Never lead to a satisfactory solution of the CSC problem or

- The same solution is found using a different insertion point.

#### **Transition Point Restrictions**

- A transition point must satisfy the following three restrictions:

- Start and end sets are disjoint (i.e.,  $t_s \cap t_e = \emptyset$ ).

- 2 End set does not include input transitions (i.e.,  $\forall t \in t_e$  .  $t \notin T_l$ ).

- Start and end sets include only concurrent transitions (i.e.,

# $TP = (\{ack\_wine+\}, \{ack\_wine-\})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

1.

$$t_s \cap t_e = \emptyset$$

2.

$$\forall t \in t_e$$

.  $t \notin T_I$

3.

$$\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$$

## $TP = (\{req\_patron+\}, \{ack\_patron+\})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

1.

$$t_s \cap t_e = \emptyset$$

2.

$$\forall t \in t_e$$

.  $t \notin T_I$

3.

$$\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$$

## $TP = (\{ack\_wine-\}, \{ack\_wine+\})$

⟨req\_wine,ack\_patron,

ack wine,req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{req\_wine-\}, \{ack\_wine-\})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{req\_patron + \}, \{req\_patron - \})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{ack\_patron + \}, \{req\_patron - \})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

### $TP = (\{ack\_wine-, req\_patron+\}, \{req\_patron-\})$

⟨req\_wine, ack\_patron, ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{req\_wine+, req\_patron-\}, \{ack\_wine+\})$

⟨req\_wine,ack\_patron,

ack wine,req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{req\_wine+, req\_patron-\}, \{ack\_wine-\})$

⟨req\_wine,ack\_patron,

ack wine,req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

### $TP = (\{req\_patron+\}, \{ack\_wine+, req\_patron-\})$

⟨req\_wine, ack\_patron, ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

### $TP = (\{req\_wine+, ack\_patron-\}, \{ack\_wine+\})$

⟨req\_wine, ack\_patron, ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

## $TP = (\{req\_patron+\}, \{req\_patron+\})$

⟨req\_wine, ack\_patron,

ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

### $TP = (\{req\_wine+, ack\_patron-\}, \{ack\_wine-\})$

⟨req\_wine, ack\_patron, ack wine, req patron⟩

- 1.  $t_s \cap t_e = \emptyset$

- 2.  $\forall t \in t_e$  .  $t \notin T_I$

- 3.  $\forall t_1, t_2 \in t_s . t_1 \parallel t_2 \ \forall t_1, t_2 \in t_e . t_1 \parallel t_2$

#### Insertion Point Restrictions

- Each  $IP = (TP_R, TP_F)$  must be checked for compatibility.

- Two TP's are incompatible when either of the following is true:

$$TP_R(t_s) \cap TP_F(t_s) \neq \emptyset$$

$TP_R(t_e) \cap TP_F(t_e) \neq \emptyset$

- An incompatible insertion point always creates an inconsistent state assignment.

- Example:

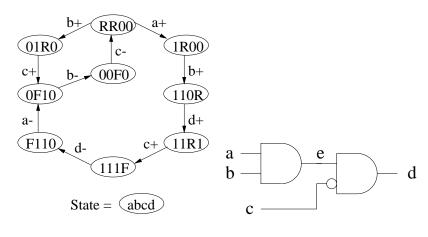

### State Graph Coloring

- Need to determine effect of inserting a state variable in an IP.

- Can be done by inserting the state signal and finding new SG.

- This approach is unnecessarily time consuming and may produce a SG with an inconsistent state assignment.

- Instead, SG is partitioned into four parts corresponding to the rising, falling, high, and low sets for the new state signal.

#### State Graph Coloring Procedure

- States in  $S(TP_R)$  are colored as rising.

- States in S(TP<sub>F</sub>) are colored as falling.

- If a state is colored both *rising* and *falling*, this IP leads to an inconsistent state assignment and must be discarded.

- All states following those colored rising before reaching any colored falling are colored as high.

- Similarly, all states between those colored as falling and those colored as rising are colored as low.

- While coloring high or low, if a state to be colored is found to already have a color, IP leads to inconsistent state assignment.

#### IP(({req\_patron+}, {req\_patron-}), ({ack\_wine-}, {ack\_wine+}))

#### IP(({req\_patron+}, {req\_patron-}), ({ack\_wine-}, {ack\_wine+}))

Rising =

$$\{\langle RR01 \rangle, \langle 1R01 \rangle, \langle R10F \rangle, \langle 110F \rangle\}$$

#### IP(({req\_patron+}, {req\_patron-}), ({ack\_wine-}, {ack\_wine+}))

$$\begin{split} \text{Rising} &= \{\langle RR01\rangle, \langle 1R01\rangle, \\ & \langle R10F\rangle, \langle 110F\rangle \} \\ \text{Falling} &= \{\langle R00R\rangle, \langle 100R\rangle, \\ & \langle RR01\rangle, \langle 1R01\rangle, \\ & \langle R10F\rangle, \langle 110F\rangle, \\ & \langle RF00\rangle, \langle 1F00\rangle, \\ & \langle R000\rangle, \langle 10F0\rangle \} \end{split}$$

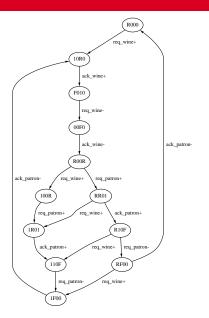

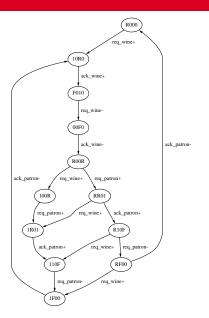

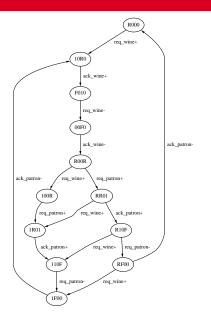

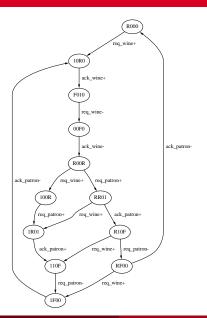

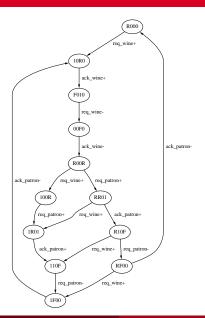

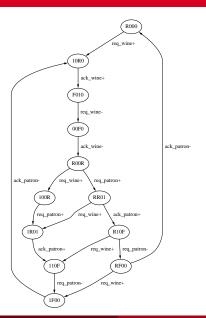

#### IP(({ack\_wine+}, {ack\_wine-}), ({req\_patron+}, {req\_patron-}))

#### IP(({ack\_wine+}, {ack\_wine-}), ({req\_patron+}, {req\_patron-}))

#### $\mathsf{IP}((\{\mathit{ack\_wine}+\}, \{\mathit{ack\_wine}-\}), (\{\mathit{req\_patron}+\}, \{\mathit{req\_patron}-\}))$

#### $IP((\{ack\_wine+\}, \{ack\_wine-\}), (\{req\_patron+\}, \{req\_patron-\}))$

#### $IP((\{ack\_wine+\}, \{ack\_wine-\}), (\{req\_patron+\}, \{req\_patron-\}))$

### **Insertion Point Primary Cost Function**

- The primary component of the cost function is the number of remaining CSC violations after a state signal is inserted.

- Eliminate from CSCV any pair of violations in which one state is colored high while the other is colored low.

- States with a USC violation may now have a CSC violation.

- For each pair of states with a USC violation (but not a CSC violation), if one is colored *rising* while the other is colored *low*, there is now a CSC violation.

- Similarly, if one is colored falling and the other is colored high, there is also a new CSC violation.

- Each new CSC violation must be added to the total remaining.

### Insertion Point Secondary Cost Functions

- The IP with the smallest sum  $|TP_R(t_e)| + |TP_F(t_e)|$ .

- The IP with the smallest sum  $|TP_R(t_s)| + |TP_F(t_s)|$ .

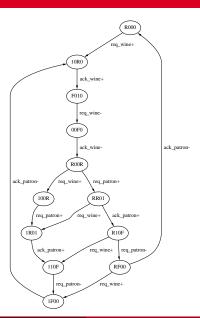

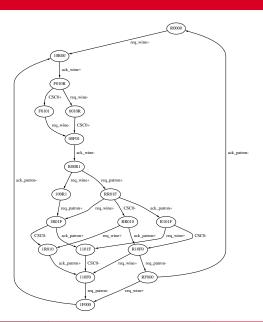

#### State Signal Insertion: Petri-net

- State signal can be inserted into a Petri-net by adding arcs from each transition in  $t_s$  to the new state signal transition.

- Arcs are also added from the new transition to each of the transitions t<sub>e</sub>.

- The same steps are followed for the reverse transition.

- The state signal is assigned an initial value based on the coloring of the initial state.

- At this point, a new SG can be found.

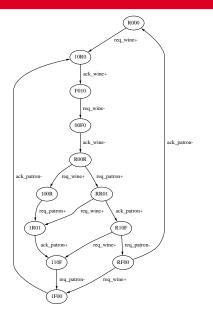

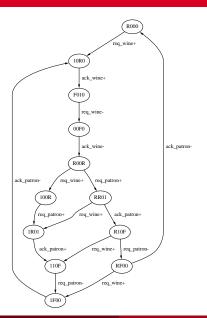

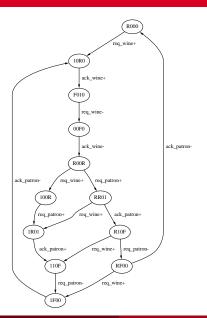

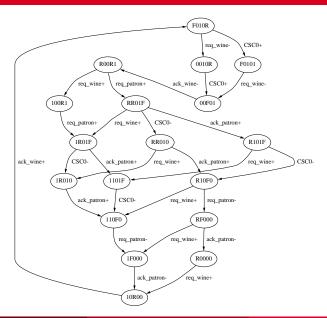

#### $\overline{\mathsf{IP}((\{\mathit{ack\_wine}+\}, \{\mathit{ack\_wine}-\}), (\{\mathit{req\_patron}+\}, \{\mathit{req\_patron}-\}))}$

## State Signal Insertion: State Graph

- Alternatively, the new SG could be found directly.

- Each state in the original SG is extended to include new signal.

- If a state is colored low, then the new signal is '0'.

- If a state is colored high, then the new signal is '1'.

- If a state is colored *rising* then it must be split into two new states, one

with new signal 'R' and the other has it as '1'.

- If a state is colored *falling* then it must be split into two new states, one has the new signal 'F' and the other has it as '0'.

## **CSC Solver Algorithm**

```

csc solver (SG)

CSCV = find csc violations(SG);

if (|CSCV| = 0) return SG;

best = |CSCV|;

best<sub>IP</sub> = (0,0);

TP = find all transition points(SG);

foreach TP_R \in TP

foreach TP_F \in TP

if IP = (TP_R, TP_F) is legal then

CSG = color\_state\_graph(SG, TP_R, TP_F);

CSCV = find csc violations(CSG);

if (CSG \text{ is consistent}) and ((|CSCV| < \text{best})) or

((|CSCV|=best) and (cost(IP) < cost(best_{IP})))) then

best = |CSCV|;

best<sub>IP</sub> = (TP_B, TP_F);

SG = insert state signal(SG, best_{IP});

SG = \csc solver(SG);

return SG;

```

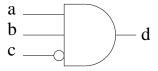

#### Hazard-free Logic Synthesis

- Requires modified minimization to obtain hazard-free logic.

- Modifications needed are dependent upon technology.

- We consider the following technologies:

- Complex gates

- @ Generalized C-elements

- Basic gates

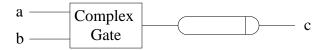

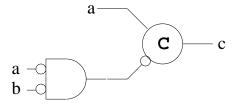

#### **Atomic Gate Implementation**

- Assume that each output to be synthesized is implemented using a single complex atomic gate.

- A gate is atomic when its delay is modeled by a single delay element connected to its output.

## **Atomic Gate Logic Synthesis**

- On-set for a signal u is the set of states in which u is excited to rise or stable high.

- Off-set is set of states in which u is excited to fall or stable low.

- DC-set is the set of all unreachable states, or equivalently those states not included in either the on-set or off-set.

$$\begin{array}{lcl} \textit{ON-set} &=& \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ES}(u+) \cup \textit{QS}(u+))\} \\ \textit{OFF-set} &=& \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ES}(u-) \cup \textit{QS}(u-))\} \\ \textit{DC-set} &=& \{0,1\}^{|\textit{N}|} - (\textit{ON-set} \cup \textit{OFF-set}) \end{array}$$

- Find primes using recursive procedure described earlier.

- Setup and solve a covering problem.

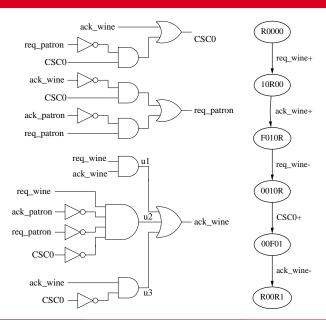

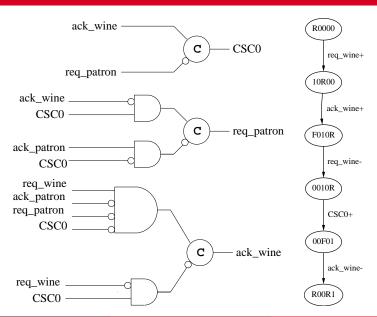

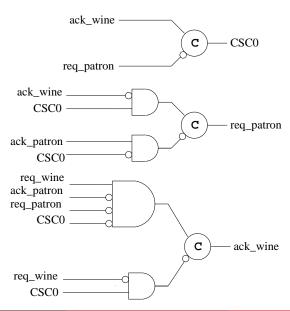

#### Passive/Active Wine Shop: Atomic Gate

## Atomic Gate: Example (Ack\_Wine)

```

\begin{array}{lll} \textit{ON-set} &=& \{10000, 10100, 00100, 10101\} \\ \textit{OFF-set} &=& \{00101, 00001, 10001, 00011, 10011, 01011, 00010, \\ && 10010, 01010, 11010, 01000, 11000, 11011, 00000\} \\ \textit{DC-set} &=& \{00110, 00111, 01001, 01100, 01101, 01110, 01111, \\ && 10110, 10111, 11001, 11100, 11101, 11110, 11111\} \end{array}

```

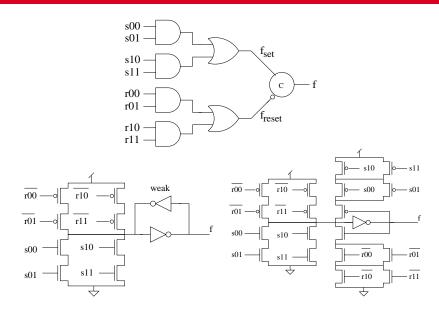

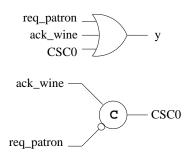

## Passive/Active Shop: Atomic Gate Circuit

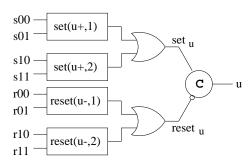

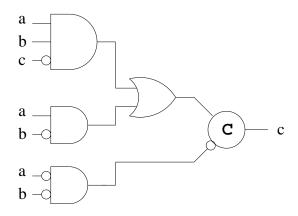

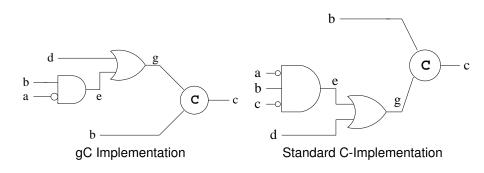

#### Generalized C-Elements

## gC Logic Synthesis

- Two minimization problems must be solved for each signal u: set of the function (i.e., set(u)) and reset (i.e., reset(u)).

- For *set*(*u*):

- On-set is states in which u is excited to rise.

- Off-set is states in which u is excited to fall or is stable low.

- DC-set is stable high and unreachable states.

- Stable high states are don't cares, since once a gC is set its feedback holds its state.

$$\begin{array}{lcl} \textit{ON-set} & = & \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ES}(u+)\} \\ \textit{OFF-set} & = & \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ES}(u-) \cup \textit{QS}(u-))\} \\ \textit{DC-set} & = & \{0,1\}^{|\textit{N}|} - (\textit{ON-set} \cup \textit{OFF-set}) \end{array}$$

# gC Logic Synthesis

- For reset(u):

- On-set is states in which u is excited to fall.

- Off-set is states in which *u* is either rising or high.

- DC-set is stable low and unreachable states.

$$\begin{array}{lcl} \textit{ON-set} & = & \{\lambda_{S}(s) \mid s \in (\textit{ES}(u-)\} \\ \textit{OFF-set} & = & \{\lambda_{S}(s) \mid s \in (\textit{ES}(u+) \cup \textit{QS}(u+))\} \\ \textit{DC-set} & = & \{0,1\}^{|\textit{N}|} - (\textit{ON-set} \cup \textit{OFF-set}) \end{array}$$

Can now apply standard methods to find a minimum number of primes to implement the set and reset functions.

# Passive/Active Wine Shop: gC

#### gC Circuit: Example

```

\begin{array}{lll} \textit{ON-set} &=& \{10000\} \\ \textit{OFF-set} &=& \{00101,00001,10001,00011,10011,01011,00010,\\ &&& 10010,01010,11010,01000,11000,11011,00000\} \\ \textit{DC-set} &=& \{00110,00111,01001,01100,01101,01110,01111,\\ &&& 10110,10111,11001,11100,11101,11110,11111,\\ &&& 10100,00100,10101\} \end{array}

```

$P = \{1-1--,-11--,-11-,-1-0,-1-01,10-00\}$

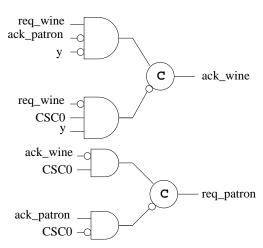

## Passive/Active Shop: gC Circuit

# A Simple Example

## Combinational Optimization

- If set(u) is on in all states in which u should be rising or high, then the state holding element can be removed.

- Implementation for u is equal to the logic for set(u).

- If reset(u) is on in all states in which u should be falling or low, then the signal u can be implemented with reset(u).

# **Combinational Optimization**

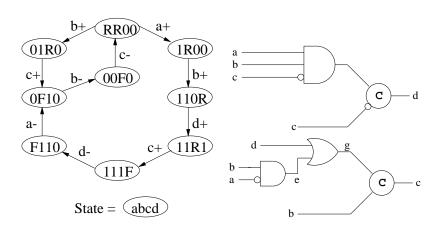

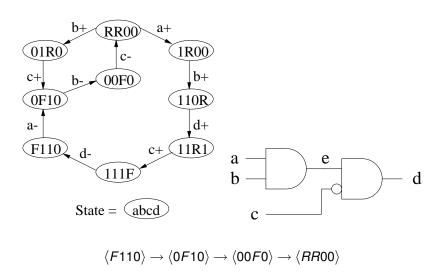

#### Gate-Level Hazard

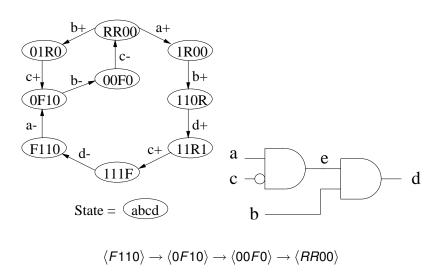

$$\langle F110\rangle \rightarrow \langle 0F10\rangle \rightarrow \langle 00F0\rangle$$

#### Standard C-implementation

- Structure similar to gC-implemenation, but built differently.

- Each AND gate, called a *region function*, implements a single (or possibly a set of) excitation region(s) for the signal *u*.

- In gC-implementation, an excitation region can be implemented by multiple product terms.

- A region function may need to be implemented using SOP.

#### **Region Function Operation**

- Each region function must:

- Turn on only when it enters a state in its excitation region.

- Turn off monotonically sometime after the signal *u* changes.

- Must stay off until the excitation region is entered again.

- To guarantee this behavior, each region function must satisfy certain correctness constraints.

- Requires a modified logic minimization procedure.

#### **Region Function Covers**

- Each region function is implemented using a single atomic gate, corresponding to a *cover* of an excitation region.

- A cover C(u\*,k) is a set of states for which the corresponding region function evaluates to one.

- First present a method in which each region function only implements a single excitation region.

- Later extend the method to allow a single region function to implement multiple excitation regions to promote gate sharing.

#### Correctness Constraints: Intuition

- Each region function can only change when it is needed to actively drive the output signal to change.

- Consider a region function for a set region:

- Gate turns on when circuit enters a state in the set region.

- When region function changes to 1, it excites the OR gate.

- When the OR gate changes to 1 in excites the C-element (assuming the reset network is low) to set u to 1.

- Only after *u* rises can the region function be excited to fall.

- The region function then must fall monotonically.

- The signal u will not be able to fall until the region function has fallen and the OR gate for the set network has fallen.

- Once region function falls, it cannot be excited again until the circuit again enters a state in this set region.

#### **Covering Constraint**

- The reachable states in a correct cover must include the entire excitation region.

- It must not include any states outside the union of the excitation region and associated quiescent states.

$$ER(u*,k) \subseteq [C(u*,k) \cap S] \subseteq [ER(u*,k) \cup QS(u*)]$$

#### **Entrance Constraint**

A cover must only be entered through excitation region states.

$$[(s_i,t,s_j)\in\delta\wedge s_i\not\in \textit{C}(\textit{u}*,\textit{k})\wedge s_j\in\textit{C}(\textit{u}*,\textit{k})]\Rightarrow s_j\in\textit{ER}(\textit{u}*,\textit{k})$$

## **Excitation Region Implicants**

- Goal of logic minimization is to find an optimal SOP for each region function that satisfies the definition of a correct cover.

- An implicant of an excitation region is a product that may be part of a correct cover.

- c is an implicant of an excitation region ER(u\*,k) if the reachable states covered by c are a subset of the states in the union of the excitation region and associated quiescent states.

$$[c \cap S] \subseteq [ER(u*,k) \cup QS(u*)].$$

# Gate Level Logic Synthesis: Set Regions

- For each set region ER(u+,k):

- On-set is those states in ER(u+,k).

- Off-set includes states in which u is falling or low, and also the states outside this excitation region where u is rising.

- This additional restriction is necessary to make sure that a region function can only turn on in its excitation region.

$$\begin{array}{lcl} \textit{ON-set} & = & \{\lambda_{S}(s) \mid s \in (\textit{ER}(u+,k)\} \\ \textit{OFF-set} & = & \{\lambda_{S}(s) \mid s \in (\textit{ES}(u-) \cup \textit{QS}(u-)) \cup \\ & & (\textit{ES}(u+) - \textit{ER}(u+,k))\} \\ \textit{DC-set} & = & \{0,1\}^{|N|} - (\textit{ON-set} \cup \textit{OFF-set}) \end{array}$$

## Gate Level Logic Synthesis: Reset Regions

• For a reset region ER(u-,k):

$$\begin{array}{lcl} \textit{ON-set} & = & \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ER}(u-,k)\} \\ \textit{OFF-set} & = & \{\lambda_{\mathcal{S}}(s) \mid s \in (\textit{ES}(u+) \cup \textit{QS}(u+)) \cup \\ & & (\textit{ES}(u-) - \textit{ER}(u-,k))\} \\ \textit{DC-set} & = & \{0,1\}^{|N|} - (\textit{ON-set} \cup \textit{OFF-set}) \end{array}$$

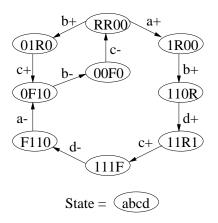

#### Gate Level Circuit: Example

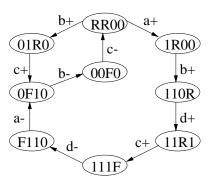

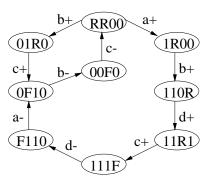

#### Gate Level Circuit: Example

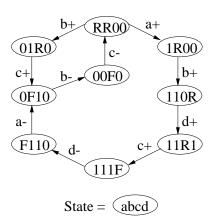

- There are two set regions for c: ER(c+,1) = 01R0 and ER(c+,2) = 11R1.

- Let's examine the implementation of ER(c+,1).

• The primes found are as follows:

$$P = \{01--,1-1-,-11-,0--1,-0-1,--11\}$$

#### Implied States

- The entrance constraint creates a set of *implied states* for each implicant c (denoted IS(c)).

- A state s is in IS(c) if it is not covered by c but due to the entrance constraint must be covered if c is part of the cover.

- A state  $s_i$  is in IS(c) for ER(u\*,k) if it is not covered by c, and  $s_i$  leads to  $s_i$  which is both covered by c and not in ER(u\*,k).

$$\mathit{IS}(c) = \{s_i \mid s_i \not\in c \land \exists s_j.(s_i, t, s_j) \in \delta \land (s_j \in c) \land (s_j \not\in \mathit{ER}(u*, k))\}$$

- This means that the product *c* becomes excited in a quiescent state instead of an excitation region state.

- If there no other product in the cover contains this implied state, the cover violates the entrance constraint.

#### Existence of a Prime Cover

- An implicant may have implied states that are outside the excitation region and the cooresponding quiescent states.

- Implied states may not be covered by any other implicant.

- If this implicant is the only prime which covers some excitation region state, then no cover can be found using only primes.

Consider prime 01--

Consider prime 01--Entered by (F110, a-, 0F10)

Consider prime 01--Entered by (F110, a-, 0F10) F110 is implied state

Consider prime 01-Entered by (F110, a-, 0F10)

F110 is implied state

Cover with 1-1- or -11-

Consider prime 01--Entered by (F110, a-, 0F10)F110 is implied state Cover with 1-1- or -11-Entered by (11R1, c+, 111F)

#### Existence of a Prime Cover: Example

abcd

Consider prime 01--Entered by (F110, a-, 0F10)F110 is implied state Cover with 1-1 or -11Entered by (11R1, c+, 111F)11R1 is implied state

#### Existence of a Prime Cover: Example

Consider prime 01--Entered by (F110,a-,0F10)F110 is implied state Cover with 1-1- or -11-Entered by (11R1,c+,111F)11R1 is implied state But it is in the OFF-set

## Candidate Implicants

- Implicant is a candidate implicant if there does not exist one which properly contains it with a subset of the implied states.

- $c_i$  is a candidate implicant if there *does not exist* an implicant  $c_j$  that satisfies the following two conditions:

$$egin{array}{ll} c_j &\supset & c_i \ IS(c_j) &\subseteq & IS(c_i). \end{array}$$

- Prime implicants are always candidate implicants, but not all candidate implicant are prime.

- An optimal cover exists using only candidate implicants.

- NOTE: similar to prime compatibles.

# Candidate Implicant Algorithm

```

candidate implicants(SG, P)

done = \emptyset

for(k = |largest(P)|; k \ge 1; k - -)

foreach(q \in P; |q| = k) enqueue(C, q)

foreach(c \in C; |c| = k)

if(IS(SG,c)=\emptyset) continue

foreach(s \in lit \ extend(c))

if(s \in done) continue

\Gamma_s = IS(SG, s)

prime = true

foreach(q \in C; |q| > k)

if (s \subset a)

\Gamma_q = IS(SG,q)

if (\Gamma_s \supseteq \Gamma_a) {

prime = false;

break

if(prime = 1) enqueue(C, s)

done = done \cup \{s\}

```

| Primes | Implied States |

|--------|----------------|

| 01     |                |

| 1-1-   |                |

| -11-   |                |

| 01     |                |

| -0-1   |                |

| 11     |                |

|        |                |

|        |                |

Chris J. Myers (Lecture 6: Muller Circuits)

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   |                |

| -11-   |                |

| 01     |                |

| -0 - 1 |                |

| 11     |                |

|        |                |

|        |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   |                |

| 01     |                |

| -0 - 1 |                |

| 11     |                |

|        |                |

|        |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     |                |

| -0-1   |                |

| 11     |                |

|        |                |

|        |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 |                |

| 11     |                |

|        |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     |                |

| 1 1111163 | implied States |

|-----------|----------------|

| 01        | F110           |

| 1-1-      | 11R1           |

| -11-      | 11R1, 01R0     |

| 01        | 0              |

| -0 - 1    | 0              |

| 11        | 11R1           |

|           |                |

Implied States

Primas

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | Ø              |

| -0-1   | 0              |

| 11     | 11R1           |

| 010-   |                |

| 01   | 1 1 1 0    |

|------|------------|

| 1-1- | 11R1       |

| -11- | 11R1, 01R0 |

| 01   | 0          |

| -0-1 | 0          |

| 11   | 11R1       |

| 010- | 0          |

|      |            |

Implied States

Primes

0.1 - -

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 011-   |                |

| State = | abcd |

|---------|------|

|---------|------|

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | Ø              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 011-   | F110           |

| State = | abcd |

|---------|------|

| State – | abcu |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 0110   |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 0110   | F110           |

| State = | (abcd) |

|---------|--------|

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 0111   |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 0111   | Ø              |

abcd

State =

| VOT      | -11- | 11R1, 01R0 |

|----------|------|------------|

| (110R)   | 01   | Ø          |

| $ _{d+}$ | -0-1 | Ø          |

| 1101     | 11   | 11R1       |

| + (11R1) | 010- | 0          |

|          | 101- |            |

| _        |      |            |

Primes

01--

Implied States F110

11R1

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0-1   | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 101-   | 0              |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0-1   | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 101-   | 0              |

| 1-10   |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 101-   | Ø              |

| 1-10   | 111F           |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0-1   | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 101-   | Ø              |

| 1-10   | 111F           |

| -110   |                |

| Primes | Implied States |

|--------|----------------|

| 01     | F110           |

| 1-1-   | 11R1           |

| -11-   | 11R1, 01R0     |

| 01     | 0              |

| -0 - 1 | 0              |

| 11     | 11R1           |

| 010-   | 0              |

| 101-   | 0              |

| 1-10   | 111F           |

| -110   | 111F. 01R0     |

### Formulating the Covering Problem

- Introduce a Boolean variable  $x_i$  for each candidate implicant  $c_i$ .

- The variable  $x_1 = 1$  when the candidate implicant is included in the cover and 0 otherwise.

- Using these variables, we can construct a product of sums representation of the covering and entrance constraints.

#### **Covering Clauses**

- A covering clause is constructed for each state s in ER(u\*, k).

- Each clause consists of disjunction of candidates that cover s.

$$\bigvee_{i:s\in c_i} x_i.$$

• ER(u\*,k) = 0100 which is included in only candidate implicants  $c_1$  (01 - -) and  $c_2$  (010 -):

$$(x_1 + x_2)$$

#### Closure Clauses

- For each candidate implicant  $c_i$ , a closure clause is constructed for each of its implied states  $s \in IS(c_i)$ .

- Each closure clause represents an implication if a candidate implicant used, its implied states must be covered.

$$\overline{X_i} \vee \bigvee_{j:s \in c_j} X_j.$$

- The candidate implicant  $c_1$  (01 ) has implied state 0110.

- 0110 included in implicants  $c_3$  (1 1–) and  $c_5$  (–11–).

$$(\overline{x_1} + x_3 + x_5)$$

• Complete formula:  $(x_1 + x_2)(\overline{x_1} + x_3 + x_5)\overline{x_3} \ \overline{x_5} \ \overline{x_8}$

#### Setting Up the Constraint Matrix

- Find  $x_i$ 's that satisfy function with minimum cost.

- Since negated variables, the covering problem is binate.

- The constraint matrix has one row for each clause and one column for each candidate implicant.

- Rows divided into a covering section and a closure section.

- Covering section: row for each excitation region state s, with a 1 in every column with a candidate implicant that includes s.

- Closure section: row for each implied state s of each candidate implicant  $c_i$ , with a 0 in the column corresponding to  $c_i$  and a 1 in each column with a candidate implicant  $c_i$  that covers s.

# Constraint Matrix for ER(c+,1)

|   | 01 | 010- | 1-1- | 101- | -11- | 01 | -0 - 1 | 11 | 1-10 | -110 |

|---|----|------|------|------|------|----|--------|----|------|------|

| 1 | 1  | 1    | _    | _    | _    | _  | _      | _  | _    | _    |

| 2 | 0  | _    | 1    | _    | 1    | _  | _      | _  | 1    | 1    |

| 3 | _  | _    | 0    | _    | _    | _  | _      | _  | _    | _    |

| 4 | _  | _    | _    | _    | 0    | _  | _      | _  | _    | _    |

| 5 | _  | _    | _    | _    | _    | _  | _      | 0  | _    | _    |

| 6 | _  | _    | 1    | _    | 1    | _  | _      | 1  | 0    | _    |

| 7 | _  | _    | 1    | _    | 1    | _  | _      | 1  | _    | 0    |

# A Simple Example

## Combinational Optimization

Can remove the C-element when the covers for the set function for a signal u include all states where u is rising or high.

$$\bigcup_{I} C(u+,I) \supseteq ER(u+,I) \cup QS(u+)$$

Or the covers for the reset function include all states where u is falling or low.

$$\bigcup_{I} \textit{C}(\textit{u}-,\textit{I}) \supseteq \textit{ER}(\textit{u}-,\textit{I}) \cup \textit{QS}(\textit{u}-)$$

### **Gate Sharing**

- Single gate can implement multiple excitation regions.

- Need to modify the covering constraint to allow the cover to include states from other excitation regions.

$$ER(u*,k) \subseteq [C(u*,k) \cap S] \subseteq \left[\bigcup_{l} ER(u*,l) \cup QS(u*)\right]$$

Entrance constraint must be modified to allow the cover to be entered from any corresponding excitation region state.

$$[(s_i,t,s_j)\in\delta\wedge s_i\not\in \textit{C}(\textit{u}*,\textit{k})\wedge s_j\in\textit{C}(\textit{u}*,\textit{k})]\Rightarrow s'\in\bigcup_{\textit{I}}\textit{ER}(\textit{u}*,\textit{I})$$

Additional constraint is now necessary to guarantee that a cover either includes an entire excitation region or none of it.

$$ER(u*,I) \not\subseteq C(u*,k) \Rightarrow ER(u*,I) \cap C(u*,k) = \emptyset$$

# Gate Sharing Example: SG

# Example: No Sharing

- ER(c+,1) = 100 and ER(c+,2) = 110.

- Using the earlier constraints, the primes are found to be:

$$P(c+,1) = \{10-,1-1,-11\}$$

$P(c+,2) = \{11-,1-1,-11\}$

- 10- has no implied states.

- 11- has implied state FR1 which can be covered by 1-1, but this has implied state 10R which is an OFF-set state.

- Prime 11- must be expanded to 110.

# Gate Sharing Example: Original Circuit

### **Example: Sharing**

- ER(c+,1) = 100 and ER(c+,2) = 110.

- Using the new constraints, the primes are found to be:

$$P(c+,1) = \{1--,-11\}$$

$P(c+,2) = \{1--,-11\}$

# Gate Sharing Example: Optimized Circuit

#### The Single Cube Algorithm

- Many region functions composed of a single product, or cube.

- Now present a more efficient algorithm which finds an optimal single-cube cover for each region function, if one exists.

### The Single Cube Algorithm

```

single cube(SG, technology)

foreach u \in O

EC = find excitation cubes(SG);

foreach EC(u*,k) \in EC

TC(u*,k) = trigger cube(SG, EC(u*,k));

CS(u*,k) = \text{context signals}(SG, EC(u*,k), TC(u*,k));

V(u*,k) = \text{violations}(SG, EC(u*,k), TC(u*,k), \text{tech});

CC = \text{build cover table}(CS(u*,k), V(u*,k));

C(u*,k) = solve cover table (CC, TC(u*,k));

solution(u) = optimize logic(C);

return solution;

```

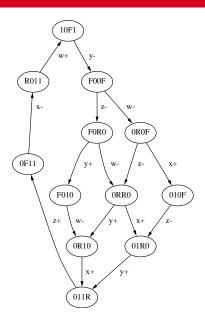

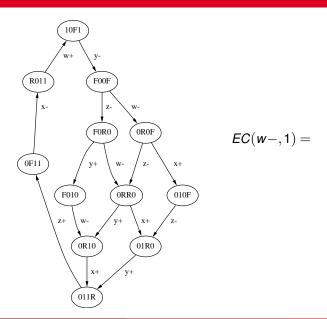

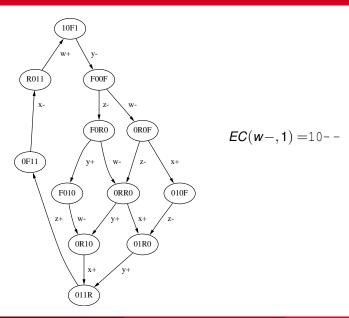

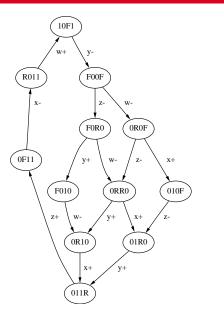

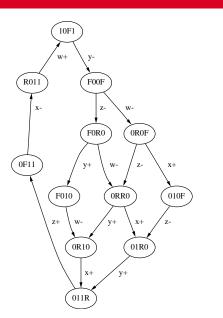

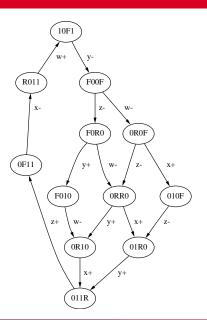

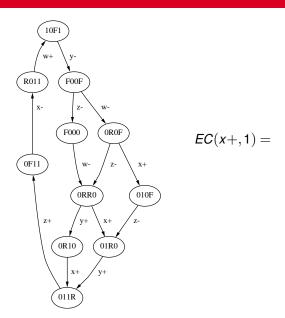

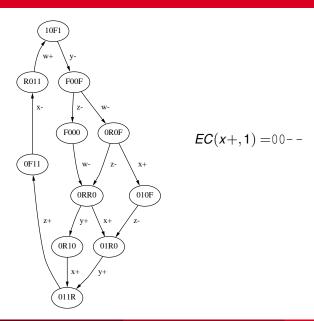

#### **Excitation Cubes**

- In a single-cube cover, all literals must correspond to signals that are stable throughout the excitation region.

- ER(u\*,k) is approximated using an excitation cube.

- The excitation cube is the supercube of the states in the excitation region and defined on each signal v as follows:

$$EC(u*,k)(v) \equiv \left\{ egin{array}{ll} 0 & ext{if } orall s \in ER(u*,k) \ . \ s(v) = 0 \ 1 & ext{if } orall s \in ER(u*,k) \ . \ s(v) = 1 \ - & ext{otherwise} \end{array}

ight.$$

- If a signal has a value of 0 or 1 in the excitation cube, the signal can be used in the cube implementing the region.

- The set of states implicitly represented by the excitation cube is always a superset of the set of excitation region states.

## **Trigger Cubes**

- The set of trigger signals for ER(u\*,k) can also be represented with a cube called a trigger cube.

- TC(u\*, v) is defined as follows for each signal v:

$$\mathit{TC}(u*,k)(v) \equiv \left\{ egin{array}{ll} s_j(v) & \mbox{ If } \exists (s_i,t,s_j) \in \delta \ . \ (t=v+ee t=v-) \land \\ & (s_i

otin \mathit{ER}(u*,k)) \land (s_j \in \mathit{ER}(u*,k)) \\ - & \mbox{ otherwise} \end{array}

ight.$$

- The single cube cover of an excitation region must contain all its trigger signals (i.e., C(u\*, k) ⊆ TC(u\*, k)).

- Therefore, all trigger signals must be stable (i.e.,  $EC(u*,k) \subseteq TC(u*,k)$ ).

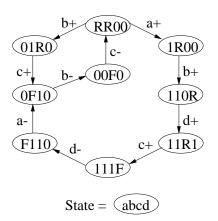

| <b>G</b> |        |

|----------|--------|

| State =  | (abcd) |

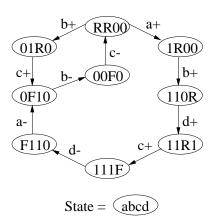

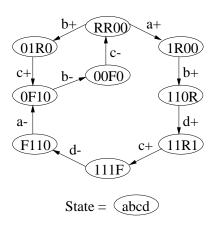

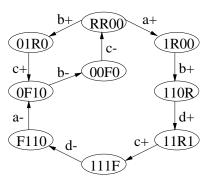

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         |          |          |

| c+,2         |          |          |

| <i>c</i> -,1 |          |          |

| d+,1         |          |          |

| d-,1         |          |          |

| State = | abcd |

|---------|------|

| State = | abcd |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     |          |

| c+,2         |          |          |

| <i>c</i> -,1 |          |          |

| d+,1         |          |          |

| d−,1         |          |          |

| State = | abcd |

|---------|------|

| State = | abcd |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     | -1       |

| c+,2         |          |          |

| <i>c</i> -,1 |          |          |

| d+,1         |          |          |

| d−,1         |          |          |

| Ctata   |        |

|---------|--------|

| State = | (abcd) |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     | -1       |

| c+,2         | 1101     |          |

| <i>c</i> -,1 |          |          |

| d+,1         |          |          |

| d−,1         |          |          |

| Ctata   | (aland) |

|---------|---------|

| State = | (abcd)  |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| <i>c</i> +,1 | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> −,1 |          |          |

| d+,1         |          |          |

| <i>d</i> −,1 |          |          |

| State = | abcd |

|---------|------|

| State – | abcu |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> -,1 | 0010     |          |

| d+,1         |          |          |

| d−,1         |          |          |

| Ctata   |        |

|---------|--------|

| State = | (abcd) |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| <i>c</i> +,1 | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> −,1 | 0010     | -0       |

| d+,1         |          |          |

| <i>d</i> −,1 |          |          |

| Ctata - | ahad   |

|---------|--------|

| State = | (abcd) |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> -,1 | 0010     | -0       |

| d+,1         | 1100     |          |

| d−,1         |          |          |

| <b>G</b> |        |

|----------|--------|

| State =  | (abcd) |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| <i>c</i> +,1 | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> −,1 | 0010     | -0       |

| d+,1         | 1100     | -1       |

| d-,1         |          |          |

| State = | abcd |

|---------|------|

| State – | abcu |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| <i>c</i> +,1 | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> -,1 | 0010     | -0       |

| d+,1         | 1100     | -1       |

| <i>d</i> −,1 | 1111     |          |

| State = | abcd |

|---------|------|

| State – | abcu |

| u∗,k         | EC(y*,k) | TC(y*,k) |

|--------------|----------|----------|

| c+,1         | 0100     | -1       |

| c+,2         | 1101     | 1        |

| <i>c</i> -,1 | 0010     | -0       |

| d+,1         | 1100     | -1       |

| d-,1         | 1111     | 1-       |

## Violating States

• Goal is to find smallest product C(u\*,k) where

$$EC(u*,k) \subseteq C(u*,k) \subseteq TC(u*,k)$$

and satisfies the required correctness constraints.

- Begin with a cube consisting only of the trigger signals.

- If this cover contains no states that violate the required correctness constraints, we are done.

- If not, context signals must be added to the cube to remove any violating states.

- For each violation, the procedure determines the choices of context signals which would exclude the violating state.

- Finding smallest set of context signals is a covering problem.

## Violating States: gC Circuits

- In gC circuits, for a set region a state is a violating state when the trigger cube intersects the falling or low sets.

- Similarly, for a reset region, a state is a violating state when the trigger cube intersects the *rising* or *high* sets.

$$\begin{array}{lcl} \textit{V}(\textit{u}+,\textit{k}) & = & \{\textit{s} \in \textit{S} \mid \textit{s} \in \textit{TC}(\textit{u}+,\textit{k}) \land \textit{s} \in \textit{ES}(\textit{u}-) \cup \textit{QS}(\textit{u}-)\} \\ \textit{V}(\textit{u}-,\textit{k}) & = & \{\textit{s} \in \textit{S} \mid \textit{s} \in \textit{TC}(\textit{u}-,\textit{k}) \land \textit{s} \in \textit{ES}(\textit{u}+) \cup \textit{QS}(\textit{u}+)\} \end{array}$$

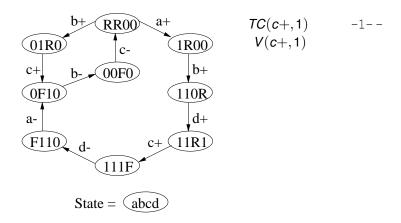

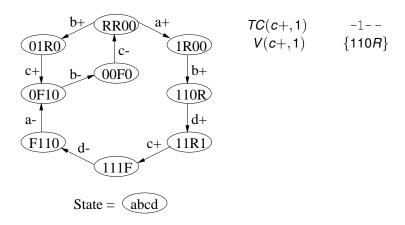

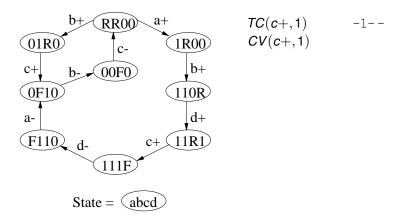

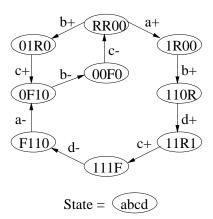

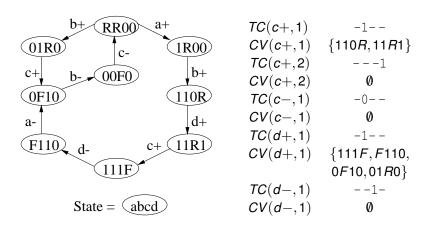

$$TC(c+,1)$$

-1--

$V(c+,1)$  {110 $R$ }

$TC(c+,2)$  ---1

$V(c+,2)$

$$TC(c+,1)$$

-1--

$V(c+,1)$  {110 $R$ }

$TC(c+,2)$  ---1

$V(c+,2)$   $\emptyset$

$$TC(c+,1)$$

-1--

$V(c+,1)$  {110 $R$ }

$TC(c+,2)$  ---1

$V(c+,2)$  0

$TC(c-,1)$  -0--

$V(c-,1)$

$$TC(c+,1)$$

$-1- V(c+,1)$   $\{110R\}$

$TC(c+,2)$   $---1$

$V(c+,2)$   $\emptyset$

$TC(c-,1)$   $-0- V(c-,1)$   $\emptyset$

$$TC(c+,1)$$

$-1- V(c+,1)$   $\{110R\}$

$TC(c+,2)$   $---1$

$V(c+,2)$   $\emptyset$

$TC(c-,1)$   $-0- V(c-,1)$   $\emptyset$

$TC(d+,1)$   $-1- V(d+,1)$

$$\begin{array}{cccc} TC(c+,1) & -1-- \\ V(c+,1) & \{110R\} \\ TC(c+,2) & ---1 \\ V(c+,2) & \emptyset \\ TC(c-,1) & -0-- \\ V(c-,1) & \emptyset \\ TC(d+,1) & -1-- \\ V(d+,1) & \{111F,F110, \\ 0F10,01R0\} \end{array}$$

$$TC(c+,1)$$

$-1- V(c+,1)$   $\{110R\}$   $TC(c+,2)$   $---1$   $V(c+,2)$   $\emptyset$   $TC(c-,1)$   $-0- V(c-,1)$   $\emptyset$   $TC(d+,1)$   $-1- V(d+,1)$   $\{111F,F110,0F10,01R0\}$   $TC(d-,1)$   $--1-$

$$TC(c+,1)$$

$-1- V(c+,1)$   $\{110R\}$

$TC(c+,2)$   $---1$

$V(c+,2)$   $\emptyset$

$TC(c-,1)$   $-0- V(c-,1)$   $\emptyset$

$TC(d+,1)$   $-1- V(d+,1)$   $\{111F,F110,$

$0F10,01R0\}$

$TC(d-,1)$   $--1 V(d-,1)$   $\emptyset$

## Context Signal Choices

- Determine context signals which remove these violating states.

- A signal is allowed to be a context signal if it is stable in the excitation cube (i.e., EC(u\*,k)(v) = 0 or EC(u\*,k)(v) = 1).

- A context signal removes a violating state when it has a different value in the excitation cube and the violating state.

- In other words, a context signal v removes a violating state s when  $EC(u*,k)(v) = \overline{s(v)}$ .

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111F

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110 $R$   $a$

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111 $F$   $c,d$

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111F c,d

F110

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111F c,d

F110 c

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110 $R$   $a$

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111 $F$   $c,d$

$F110$   $c$

0 $F10$

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110 $R$   $a$

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111 $F$   $c,d$

$F110$   $c$

0 $F10$   $a,c$

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110R a

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111F c,d

F110 c

0F10 a,c

01R0

$$EC(c+,1)$$

0100

$TC(c+,1)$  -1--

110 $R$   $a$

$EC(d+,1)$  1100

$TC(d+,1)$  -1--

111 $F$   $c,d$

$F110$   $c$

0 $F10$   $a,c$

01 $R0$   $a$

## Setting Up the Covering Problem

- The constraint matrix has a row for each violating state and a column for each context signal.

- The constraint matrix for ER(d+,1) is shown below:

#### Gate Level Circuits: Cover Violations

- Gate level circuits have covering and entrance constraints.

- For each ER(u\*,k), find all states in the initial cover, TC(u\*,k), which violate the covering constraint:

- A state s in TC(u\*,k) is a violating state if:

- The signal *u* has the same value but is not excited,

- . Is excited in the opposite direction, or

- Is excited in the same direction but the state is not in the current excitation region.

$$TC(c+,1)$$

-1--  $CV(c+,1)$  {110 $R$ ,11 $R$ 1}

#### Gate Level Circuits: Entrance Violations

- Must check state transitions for potential entrance violations.

- For each state transition  $(s_i, t, s_j)$ , this is possible when  $s_j$  is a quiescent state,  $s_i$  is in the initial cover, and  $\lambda_T(t)$  excludes  $s_i$ .

$$EV(u+,k) = \{s_j \in S \mid (s_i, v*, s_j) \in \delta \land s_j \in QS(u+) \\ \land s_j \in TC(u+,k) \land EC(u+,k)(v) = \overline{s_i(v)} \}$$

$$EV(u-,k) = \{s_j \in S \mid (s_i, v*, s_j) \in \delta \land s_j \in QS(u-) \\ \land s_j \in TC(u-,k) \land EC(u-,k)(v) = \overline{s_i(v)} \}$$

- For each potential entrance violation, a context signal must be added which excludes  $s_i$  from the cover when  $\lambda_T(t)$  is included.

- If  $\lambda_T(t)$  is a trigger signal, then the state  $s_i$  is a violating state.

- If  $\lambda_T(t)$  is a possible context signal choice, then  $s_j$  becomes a violating state when  $\lambda_T(t)$  is included in the cover.

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

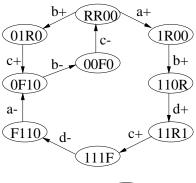

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

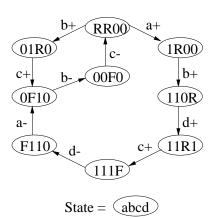

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ?

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ?

$State = \underbrace{abcd}$

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ?

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ? No 1

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ? No 1

$(11R1, c+, 111F)$ ?

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) =$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ? No 1

$(11R1, c+, 111F)$ ? No 3

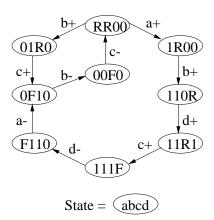

Consider each  $(s_i, v*, s_j)$

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$\begin{split} EC(c+,1) &= 0100 \\ TC(c+,1) &= -1 - - \\ EV(c+,1) &= \\ (RR00,a+,1R00)? \text{ No 1} \\ (1R00,b+,110R)? \text{ No 1} \\ (110R,d+,11R1)? \text{ No 1} \\ (11R1,c+,111F)? \text{ No 3} \\ (111F,d-,F110)? \end{split}$$

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$\begin{split} EC(c+,1) &= 0100 \\ TC(c+,1) &= -1 - - \\ EV(c+,1) &= \{\, \text{F110} \\ (RR00,a+,1R00)? \text{ No 1} \\ (1R00,b+,110R)? \text{ No 1} \\ (110R,d+,11R1)? \text{ No 1} \\ (11R1,c+,111F)? \text{ No 3} \\ (111F,d-,F110)? \text{ Yes} \end{split}$$

Consider each  $(s_i, v*, s_j)$   $s_i$  is in EV(u\*, k) when:

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) = \{F110$

$(RR00,a+,1R00)$ ? No 1

$(1R00,b+,110R)$ ? No 1

$(110R,d+,11R1)$ ? No 1

$(11R1,c+,111F)$ ? No 3

$(111F,d-,F110)$ ? Yes

$(F110,a-,0F10)$ ?

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i$$

∈  $TC(u*, k)$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$\begin{split} EC(c+,1) &= 0100 \\ TC(c+,1) &= -1 - - \\ EV(c+,1) &= \{\, F110,\, 0F10 \\ (RR00,a+,1R00)? \text{ No } 1 \\ (1R00,b+,110R)? \text{ No } 1 \\ (110R,d+,11R1)? \text{ No } 1 \\ (11R1,c+,111F)? \text{ No } 3 \\ (111F,d-,F110)? \text{ Yes} \\ (F110,a-,0F10)? \text{ Yes} \end{split}$$

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) = \{ F110, 0F10 \}$

$(RR00, a+, 1R00) ?$  No 1

$(1R00, b+, 110R) ?$  No 1

$(110R, d+, 11R1) ?$  No 1

$(11R1, c+, 111F) ?$  No 3

$(111F, d-, F110) ?$  Yes

$(F110, a-, 0F10) ?$  Yes

$(0F10, b-, 00F0) ?$

Consider each  $(s_i, v*, s_j)$

$s_j$  is in EV(u\*,k) when:

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

EC(c+,1) = 0100TC(c+,1) = -1 - - $EV(c+,1) = \{ F110, 0F10 \}$ (RR00, a+, 1R00)? No 1 (1R00, b+, 110R)? No 1 (110R, d+, 11R1)? No 1 (11R1, c+, 111F)? No 3 (111F, d-, F110)? Yes (F110, a-, 0F10)? Yes (0F10, b-, 00F0)? No 1

Consider each  $(s_i, v*, s_j)$   $s_i$  is in EV(u\*, k) when:

- 1.  $s_i \in QS(u*)$

- 2.  $s_i \in TC(u*,k)$

- 3.  $EC(u*,k)(v) = \overline{s_i(v)}$

$$\begin{split} EC(c+,1) &= 0100 \\ TC(c+,1) &= -1 - - \\ EV(c+,1) &= \{\text{F110, 0F10} \\ (RR00,a+,1R00)? \text{ No 1} \\ (1R00,b+,110R)? \text{ No 1} \\ (110R,d+,11R1)? \text{ No 1} \\ (11R1,c+,111F)? \text{ No 3} \\ (111F,d-,F110)? \text{ Yes} \\ (F110,a-,0F10)? \text{ Yes} \\ (0F10,b-,00F0)? \text{ No 1} \\ (00F0,c-,RR00)? \end{split}$$

Consider each  $(s_i, v*, s_j)$  $s_i$  is in EV(u\*, k) when:

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) = \{F110, 0F10$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ? No 1

$(11R1, c+, 111F)$ ? No 3

$(111F, d-, F110)$ ? Yes

$(F110, a-, 0F10)$ ? Yes

$(0F10, b-, 00F0)$ ? No 1

$(00F0, c-, RR00)$ ? No 1

Consider each  $(s_i, v*, s_j)$

1.

$$s_i \in QS(u*)$$

2.

$$s_i \in TC(u*,k)$$

3.

$$EC(u*,k)(v) = \overline{s_i(v)}$$

$$EC(c+,1) = 0100$$

$TC(c+,1) = -1 - -$

$EV(c+,1) = \{F110, 0F10$

$(RR00, a+, 1R00)$ ? No 1

$(1R00, b+, 110R)$ ? No 1

$(110R, d+, 11R1)$ ? No 1

$(11R1, c+, 111F)$ ? No 3

$(111F, d-, F110)$ ? Yes

$(F110, a-, 0F10)$ ? Yes