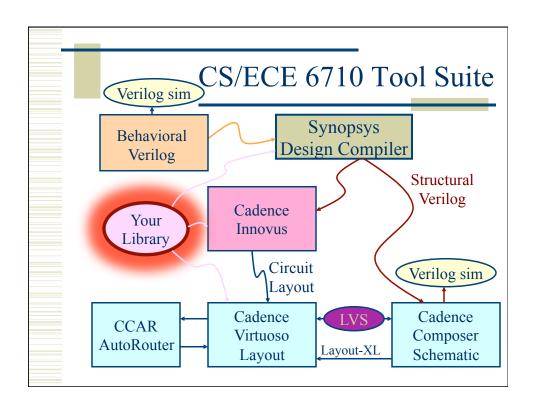

#### CAD5

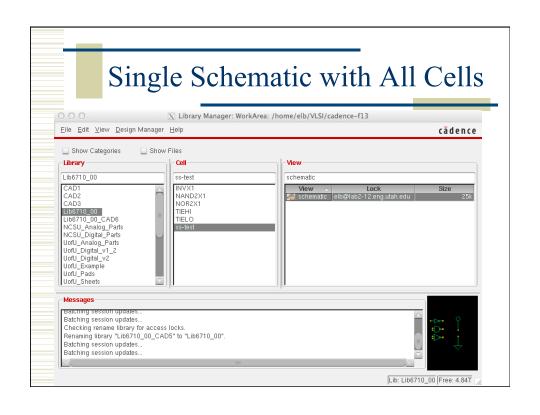

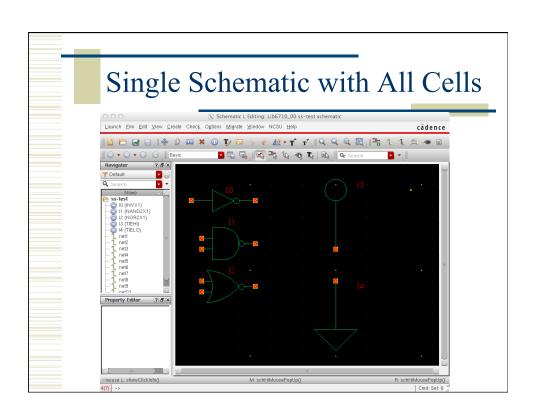

- Designing the first five cells in your library

- Multiple cell views

- Liberate library characterizer

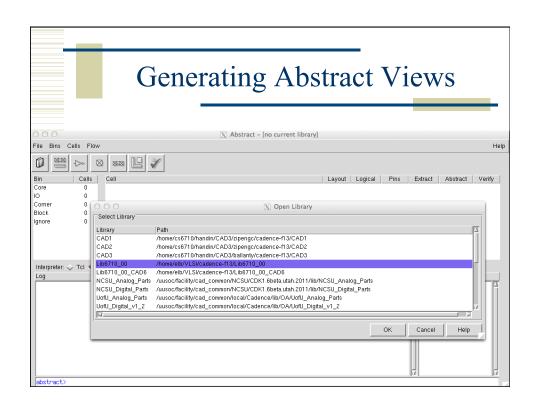

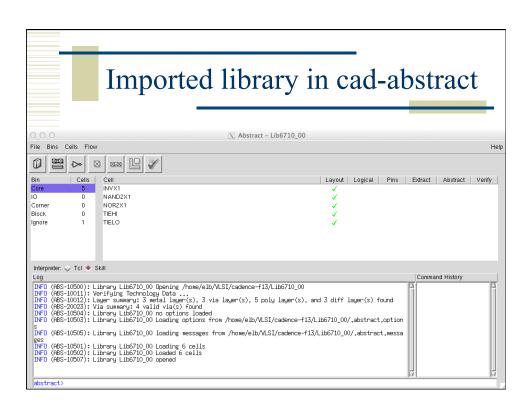

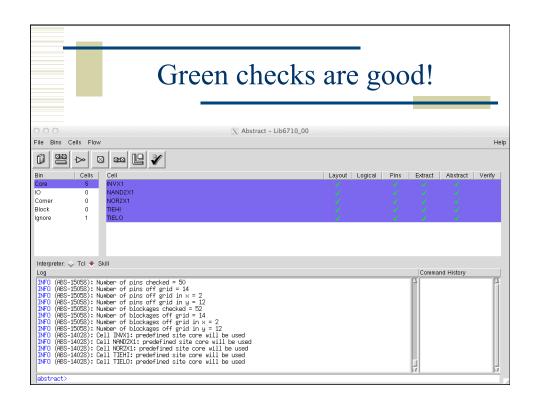

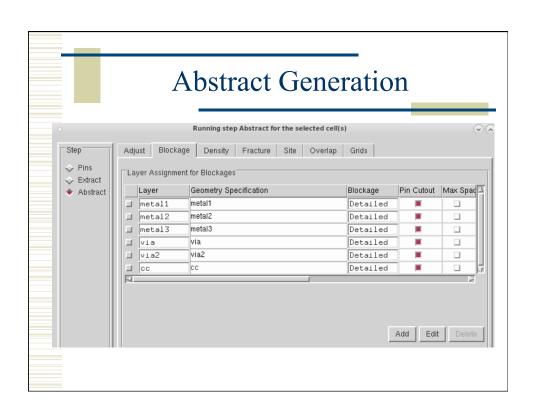

- Abstract generator

- Synopsys database generation

- Using the cells in synthesis

#### In the CAD Book

- Chapter 8 on Cell Characterization

- Section 8.1 describes .lib format

- Section 8.2 describes ELC that tool is gone...

- Instead we'll use Cadence Liberate

- Section 8.3 describes characterization by hand with Spectre (don't do it!)

- Section 8.4 describes converting from .lib to .db format (used by Synopsys Design Compiler)

- Use syn-lc instead of syn-dc...

- (.lib is used also by other tools...)

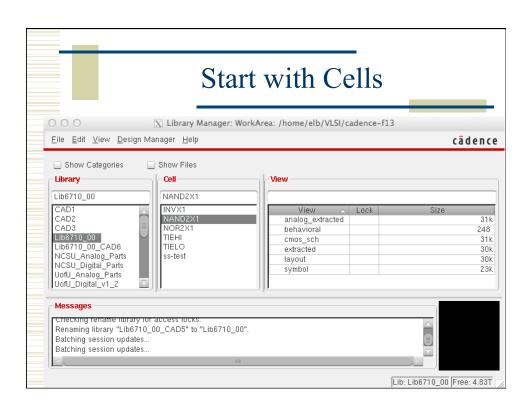

#### Start with six views of each cell

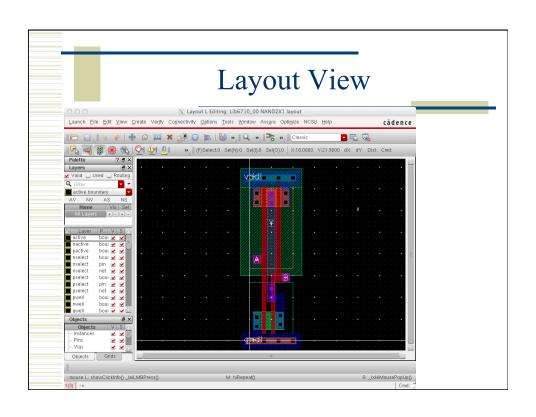

- 1. layout make sure to use the template!

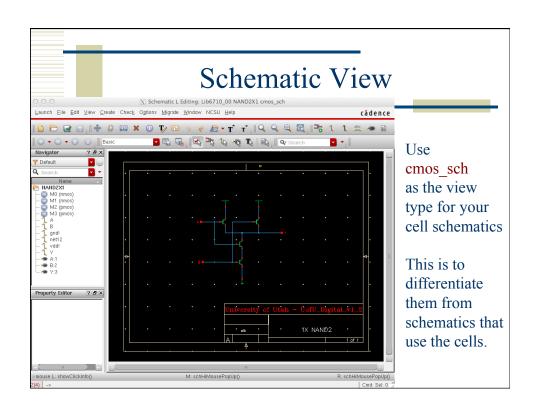

- 2. **cmos** sch use this view type for a schematic

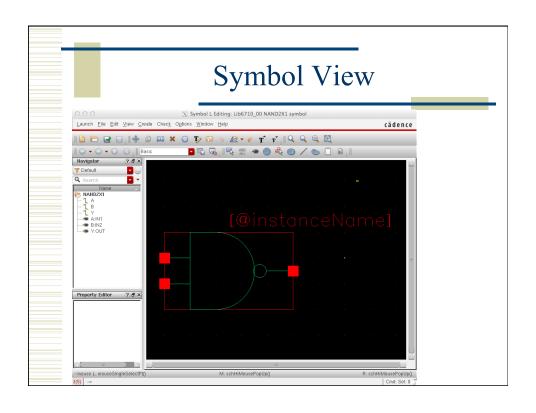

- 3. symbol Make them look nice

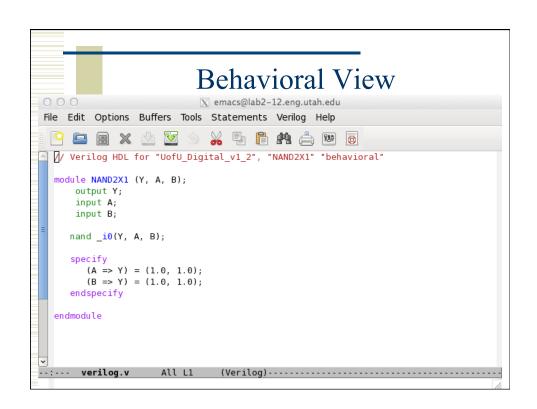

- 4. behavioral Having this view makes simulation go much faster (if you use it)

- 5. **extracted** generated from the extract processes

- 6. analog\_extracted after LVS

### Characterize the cells

- Run a set of analog (Spectre) simulations that builds a table of delay values

- Input drive vs. output load

- For all outputs

- Plus rise and fall times

- And some power information

- Cadence Liberate

- cad-lib from the bin directory

- But, don't call it directly... use additional scripts...

scs2liberate foo.scs libcells.scs

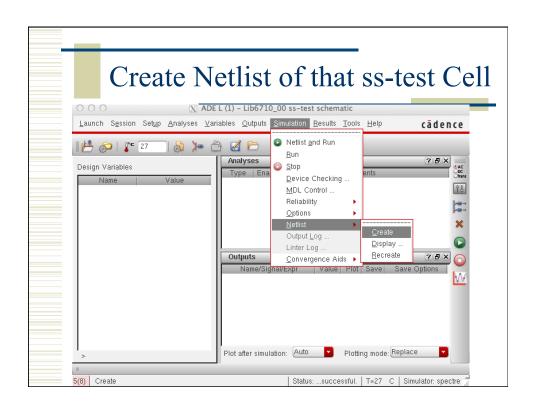

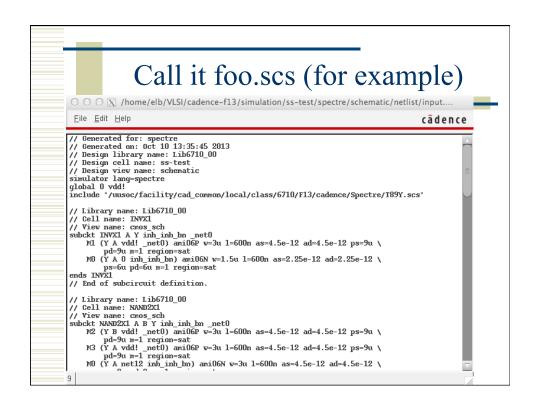

#### Convert to Liberate format

```

simulator lang=spectre

global vss vdd

subckt INVX1 A Y

M1 (Y A vdd vdd) ami06P w=6u l=600n as=9e-12 ad=9e-12 ps=15.0u \

pd=15.0u m=1 region=sat

M0 (Y A vss vss) ami06N w=3u l=600n as=4.5e-12 ad=4.5e-12 ps=9u \

pd=9u m=1 region=sat

ends INVX1

subckt NAND2X1 A B Y

M2 (Y A vdd vdd) ami06P w=6u l=600n as=9e−12 ad=9e−12 ps=15.0u \

pd=15.0u m=1 region=sat

M3 (Y B vdd vdd) ami06P w=6u l=600n as=9e−12 ad=9e−12 ps=15.0u \

pd=15.0u m=1 region=sat

M0 (Y B net12 vss) ami06N w=6u l=600n as=9e−12 ad=9e−12 \

ps=15.0u pd=15.0u m=1 region=sat

M1 (net12 A vss vss) ami06N w=6u l=600n as=9e-12 ad=9e-12 \

ps=15.0u pd=15.0u m=1 region=sat

```

#### Run Liberate

- Liberate Library Characterizer

- Figures out what each cell is (logic)

- Generates test inputs for Spectre

- Runs Spectre

- Checks output and extracts timings

- Formats the output in .lib format

- ◆ I like to make a new VLSI/Liberate directory from which to run this tool...

- cp -r /uusoc/facility/cad\_common/local/class/6710/F17/cadence/Liberate .

#### Liberate setup...

- A lib directory

- where the generated **library>.lib** file will be generated.

- A **netlist** directory

- put your **libcells.scs** file in this directory.

```

[elb@lab2-20 Liberate]$ ls

models/ README tcl/ templates/ userdata/

netlist/ run.sh* TechHeader.lef UofU_Cells.tcl

[elb@lab2-20 Liberate]$ [

```

#### Liberate setup

- A **templates** directory

- edit the UofU\_Cell\_Defs.tcl file in this directory to include cell descriptions for each of the cells you want to characterize. The UofU\_Templates.tcl file has definitions for the timing and power templates that will be used for characterization. You probably don't need to modify these unless you are using a different technology than ON Semi C5N.

```

[elb@lab2-20 Liberate]$ ls

models/ README tcl/ templates/ userdata/

netlist/ run.sh* TechHeader.lef UofU_Cells.tcl

[elb@lab2-20 Liberate]$ [

```

### Liberate setup

#### • A UofU Cells.tcl file

- edit this file to make a list of the cells that you want to characterize in this run. This could be a list of every cell described in templates/

UofU\_Cell\_Defs.tcl, or it could be a subset if you just want to try a few.

- A userdata directory

- edit the **userdata.lib** file to reflect the areas and footprints of each of the cells in your library.

```

[elb@lab2-20 Liberate]$ ls

models/ README tcl/ templates/ userdata/

netlist/ run.sh* TechHeader.lef UofU_Cells.tcl

[elb@lab2-20 Liberate]$ [

```

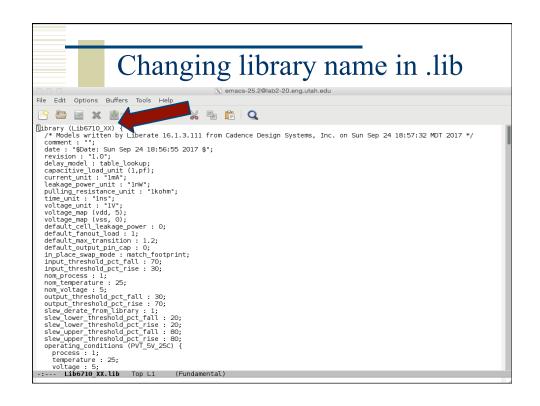

### Liberate setup

#### • A tcl directory

■ Edit the **UofU\_Char.tcl** file in this directory to change the name of the library that the tool generates. If you don't modify this, the tool will generate a file named **Lib6710\_XX.lib** by default. The **settings.tcl** file in this directory has configuration commands for the Spectre simulator. You won't need to modify this file at all.

```

[elb@lab2-20 Liberate]$ ls

models/ README tcl/ templates/ userdata/

netlist/ run.sh* TechHeader.lef UofU_Cells.tcl

[elb@lab2-20 Liberate]$ ∏

```

### Liberate setup

- A models directory

- Has the Spectre model files for the ami06N and ami06P transistors used by in your netlist.

- A run.sh shell script

- This calls the cad-lib Liberate script with the appropriate input files, and makes a copy of the log information in a **Liberate.log** file.

```

[elb@lab2-20 Liberate]$ ls

models/ README tcl/ templates/ userdata/

netlist/ run.sh* TechHeader.lef UofU_Cells.tcl

[elb@lab2-20 Liberate]$ [

```

Liberate tutorial on Canvas...

```

Torminal — sub — 150-28

Sep 26 16:36:12 Thread 0: Cell-NAND2X1 (180%) Pin — Related — combinational leakage_power ...

Sep 26 16:36:12 Thread 0: Cell-NAND2X1 (180%) Pin — Related — combinational leakage_power ...

Performance statistics for NAND2X1: Spectre cpu time = 1.2 seconds, total cpu time = 1.3 seconds, wall clock time = 9.0 seconds.

Characterizing N082X1 (2)

Sep 26 16:36:12 Thread 0: Cell-NOR2X1 (20%) Pin-Y Related-A combinational rise_transition ...

Sep 26 16:36:12 Thread 0: Cell-NOR2X1 (62%) Pin-Y Related-B combinational fill_transition ...

Sep 26 16:36:12 Thread 0: Cell-NOR2X1 (38)% Pin-Y Related-B combinational fill_transition ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (37%) Pin-A Related-B combinational fill_transition ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (39%) Pin-A Related-B combinational fill_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational fill_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational fill_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16:36:13 Thread 0: Cell-NOR2X1 (100%) Pin-B Related-B combinational leakage_power ...

Sep 26 16

```

```

Terminal — ash — 106-28

INFO: Write Liberty

LIBERATE parameter "mc.scm.mult.stops.cog.mode" set to '0'

LIBERATE parameter "cscm.mult.stops.cog.mode" set to '0'

LIBERATE parameter "cscm.mult.stops.cog.mode" set to '0'

LIBERATE parameter "cscm.mode" set to '0'

WARNING (LIB-5015): (ortita.librory): The existing library file '/home/elb/VLSI/Liberate-test/libtast/lib/Lib6710_XX.lib' was renomed to '/home/elb/VLSI/Liberate-test/libtast/lib/Lib6710_XX.lib' was renomed to '/home/elb/VLSI/Liberate-test/libtast/lib/Lib6710_XX.lib' stored at Tue Sep 26 16:36:14 MDT 2017

WINTING .lib for cell MADOXI

WINTING .lib for cell LIBLO

LIBERATE parameter "csct_coat_be_reduction" set to '1'

Number of parameter lost .s to the coat of the cell Madoxi

Liberate for library home/elb/VLSI/Liberate-test/libtast/lib/Lib6710_XX.lib at Tue Sep 26 16:36:15 MDT 2017

LIBERATE parameter "wintle.sens.co.change' set to '1'

Peck memory upage: 54 MB

Wall time : 0.00 hours (17.00 seconds)

LIBERATE parameter "wintle.sens.co.change' set to '1'

LIBERATE parameter "wintle.sens.co.co.co.co.co.change' set to '1'

LIBERATE parameter "wintle.sens.co.co.co.co.co.co.co.co.co.co

```

```

X emacs-25.2@lab2-20.eng.utah.edu

File Edit Options Buffers Tools Help

聲 🛅 🗃 🗶 🏰 Save | 🧠 Undo | 🗼 🖷 🖺 | 🔾

dell (INVX1) {

area : 129.6;

cell_footprint : "INV";

cell_leakage_power : 0.0500074;

pg_pin (vdd) {

pg_type : primary_power;

voltage_name : "vdd";

}

pg_pin (vss) {

pg_type : primary_ground;

voltage_name : "vss";

ĺeakage_power () {

value : 0.0500012;

when : "(A * !Y)";

related_pg_pin : vdd;

leakage_power () {

value : 0.0500137;

when : "(!A * Y)";

related_pg_pin : vdd;

leakage_power () {

value : 0.0500074;

related_pg_pin : vdd;

pin (Y) {

pin (Y) {

direction : output;

function : "!A";

min_capacitance : 0.01;

power_down_function : "(!vdd) + (vss)";

related_ground_pin : vss;

-:-- CAD6.lib 52% L5242 (Fundamental)

```

syn-lc

## Converting .lib to .db

```

[elb8lab2-20 lib]$ syn-lc

Using setup-synopsys from S17

Assuming your OS is and64

You are now set up to run the synopsys tools.

Working directory is /home/elb/VLSI/Liberate/lib

Library Compiler (TM)

DesignWare (R)

Version M-2016.12-SF3 for linux64 - Apr 13, 2017

Copyright (c) 1988 - 2017 Synopsys, Inc.

This software and the associated documentation are proprietary to Synopsys, Inc.

This software may only be used in accordance with the terms and conditions

of a written license agreement with Synopsys, Inc. All other use, reproduction,

or distribution of this software is strictly prohibited.

Initializing...

lc shell> read lib Lib6710 XX.lib

Reading '/home/elb/VLSI/Liberate/lib/Lib6710 XX.lib' ...

Warning: Line 1, The 'default input pin cap' attribute is not specified. Using 1.00. (LBDB-172)

Warning: Line 1, The 'default leakage power attribute is not specified. Using 0.00. (LBDB-172)

Warning: Line 10, Cell 'INNX', The cell leakage power attribute of the 'INNX' cell is redundant

and not used in the leakage power modeling. (LBDB-644)

Warning: Line 25, Cell 'INNX', The cell leakage power attribute of the 'NAND2X1' cell is redundant

and not used in the leakage power modeling. (LBDB-644)

Table710 XX' read successfully

```

#### syn-lc

## Converting .lib to .db

```

lc shell> write lib Lib6710_XX -o Lib6710_XX.db Wrote the

'Lib6710_XX' library to '/home/elb/VLSI/Liberate/lib/Lib6710_XX.db' successfully

1

lc shell> exit Memory usage for this session 19 Mbytes.

CPU usage for this session 0 seconds ( 0.00 hours ).

Thank you...

[elb@lab2-20 lib]$

```

#### In the CAD Book

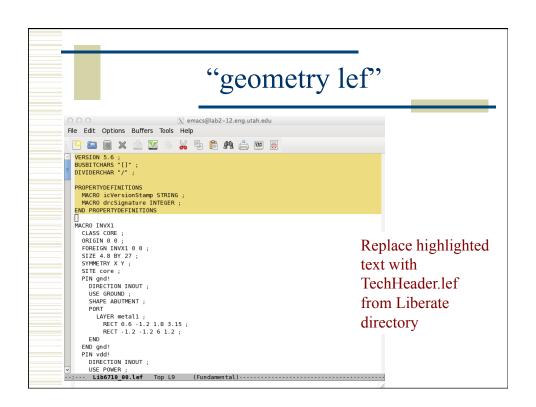

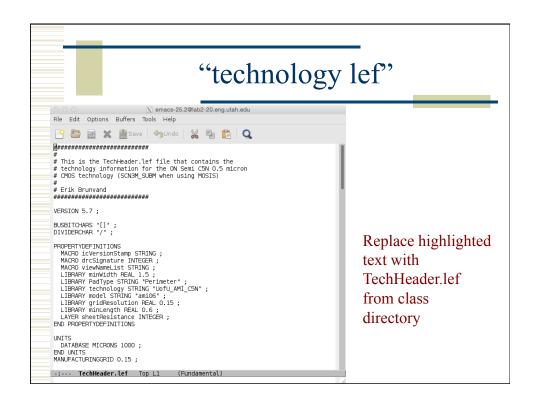

- ◆ Chapter 10 Abstract Generation

- Abstract views are used by place and route

- Eventually they are captured in a .lef file that describes the place and route geometry

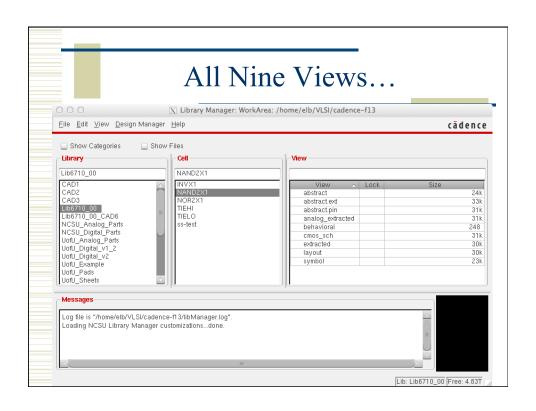

# Final CAD5 Files...

- Nine views of every cell

- abstract, abstract.ext, abstract.pin, analog\_extracted, behavioral, cmos\_sch, extracted, layout, symbol

- DRC and LVS-checked, and simulated

- Three versions of the library description

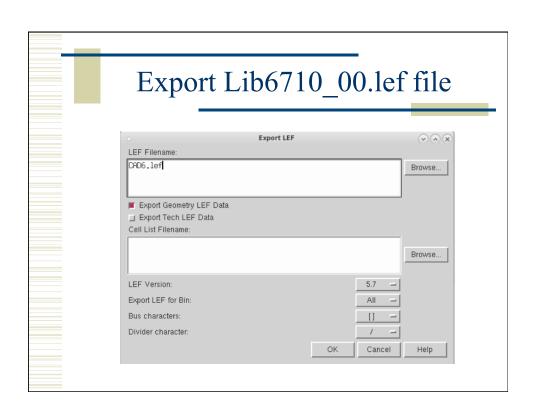

- Lib6710 00.lib // timing information

- Lib6710\_00.db // design compiler target lib

- Lib6710 00.lef // place and route info

```

addsub dc.v

module addsub ( a, b, addnsub, result );

input [7:0] a;

input [7:0] b;

output [8:0] result;

input addnsub;

wire n26, n27, n28, n29, n30, n31, n32, n33, n34, n35, n36, n37, n38, n39,

n40, n41, n42, n43, n44, n45, n46, n47, n48, n49, n50, n51, n52, n53,

n54, n55, n56, n57, n58, n59, n60, n61, n62, n63, n64, n65, n66, n67,

NAND2X1 U33 ( .A(n26), .B(n27), .Y(result[8]));

NAND2X1 U34 ( .A(b[7]), .B(n28), .Y(n27));

NAND2X1 U35 ( .A(n29), .B(n30), .Y(n28) );

NOR2X1 U36 ( .A(n31), .B(n32), .Y(n29) );

NOR2X1 U216 ( .A(n188), .B(a[0]), .Y(n175));

NAND2X1 U217 ( .A(a[0]), .B(n188), .Y(n202) );

INVX1 U218 ( .A(b[0]), .Y(n188) );

endmodule

```

#### addsub dc.v.rep Operating Conditions: typical Library: Lib6710\_00 Wire Load Model Mode: top Startpoint: b[1] (input port) Endpoint: result[8] (output port) Path Group: (none) Path Type: max Incr input external delay 0.00 r b[1] (in) 0.00 0.00 r U198/Y (NOR2X1) 0.50 0.50 f U194/Y (NOR2X1) 0.86 r 0.36 U34/Y (NAND2X1) 0.25 10.16 f U33/Y (NAND2X1) 0.24 10.40 r result[8] (out) 0.00 10.40 r data arrival time (Path is unconstrained)

```

addsub_dc.v.rep

Library(s) Used:

Lib6710 00 (File: /home/elb/VLSI/cadence-f13/syn-f13/CAD5test/

Lib6710_00.db)

Number of ports:

26

Number of nets:

203

Number of cells:

Number of combinational cells:

186

Number of sequential cells:

0

Number of macros:

37

Number of buf/inv:

Number of references:

```

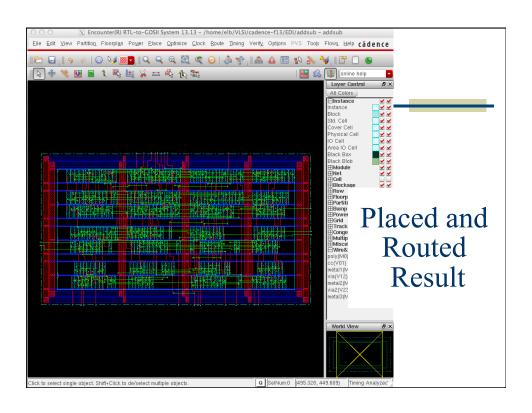

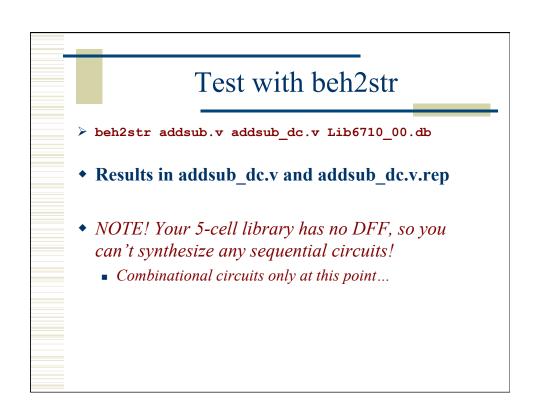

# Summary

- You now have a library that is fully functional

- BUT only on combinational circuits

- No DFF yet!

- Every step of the way requires extreme care to get things exactly right

- No trick to finding the right answer

- The point is to practice working with the data & tools

```

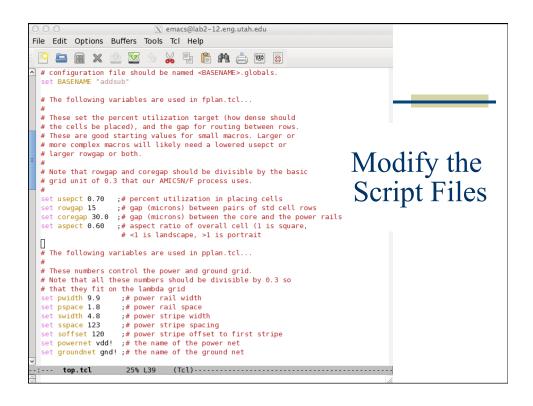

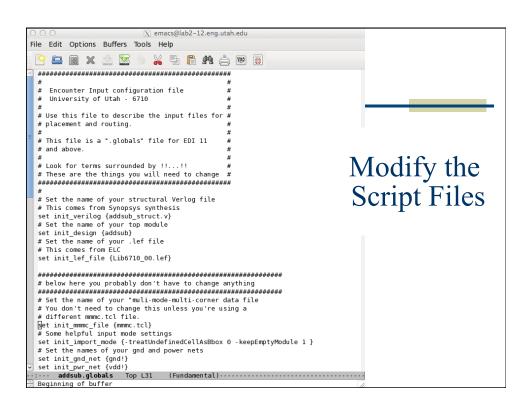

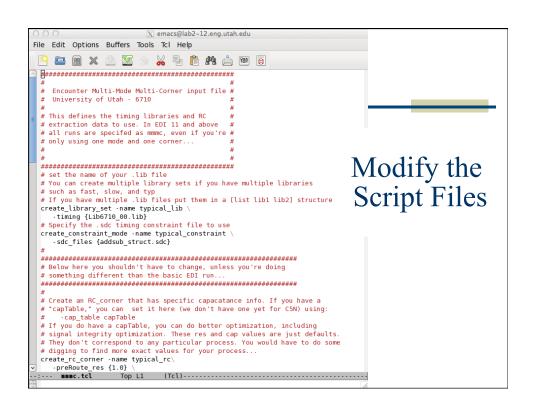

Look ahead to Innovus

[elb@lab2-12 addsub]$ ll -t

total 132

-rw-r--r-- 1 elb cs-rsrch 1522 Oct 10 2013 addsub.globals

-rw-r--r-- 1 elb cs-rsrch 3814 Oct 10 2013 top.tcl

-rw-r--r-- 1 elb cs-rsrch 2618 Oct 10 2013 mmmc.tcl

-rw-r--r-- 1 elb cs-rsrch 280 Oct 10 16:39 Lib6710_00.v

-rw-r--r-- 1 elb cs-rsrch 22736 Oct 10 16:39 Lib6710_00.lib

-rw-r--r-- 1 elb cs-rsrch 31744 Oct 10 16:39 Lib6710_00.db

-rw-r--r-- 1 elb cs-rsrch 11919 Oct 10 16:39 Lib6710_00.lef

-rw-r--r- 1 elb cs-rsrch 3413 Oct 10 16:39 addsub_struct.sdc

-rw-r--r-- 1 elb cs-rsrch 11742 Oct 10 16:39 addsub_struct.v

-rw-r--r-- 1 elb cs-rsrch 2016 Oct 10 16:37 verify.tcl

-rw-r--r-- 1 elb cs-rsrch 3005 Oct 10 16:37 route.tcl

-rw-r--r-- 1 elb cs-rsrch 2394 Oct 10 16:37 pplan.tcl

-rw-r--r-- 1 elb cs-rsrch 1940 Oct 10 16:37 place.tcl

-rw-r--r-- 1 elb cs-rsrch 971 Oct 10 16:37 fplan.tcl

-rw-r--r-- 1 elb cs-rsrch 1641 Oct 10 16:37 cts.tcl

[elb@lab2-12 addsub]$ [

```