## **Layout Basics**

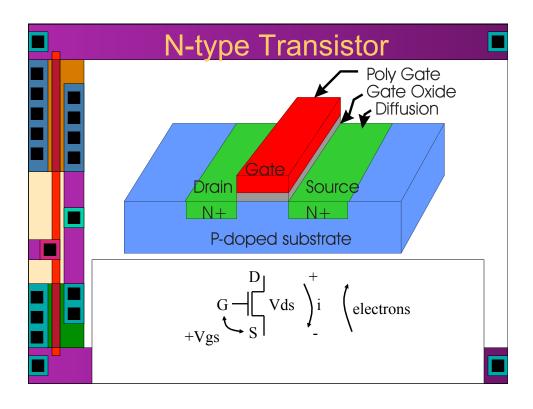

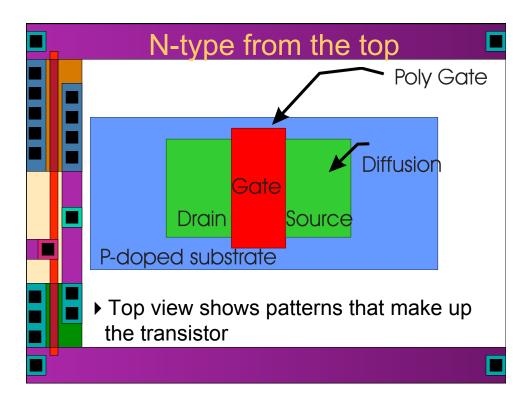

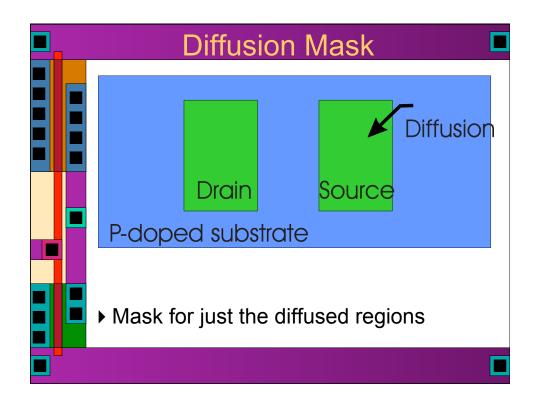

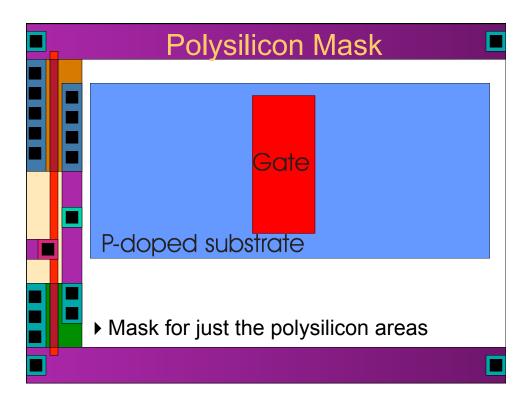

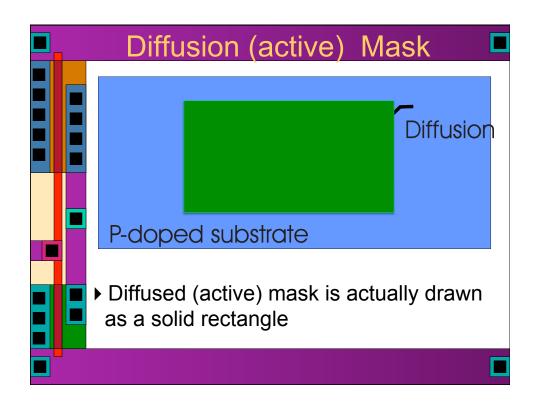

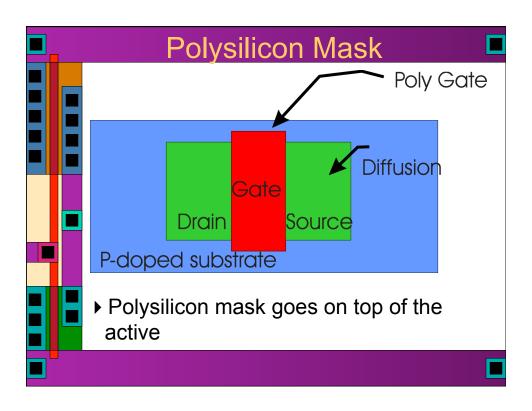

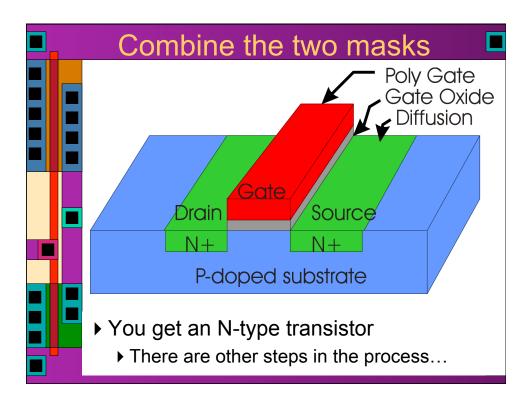

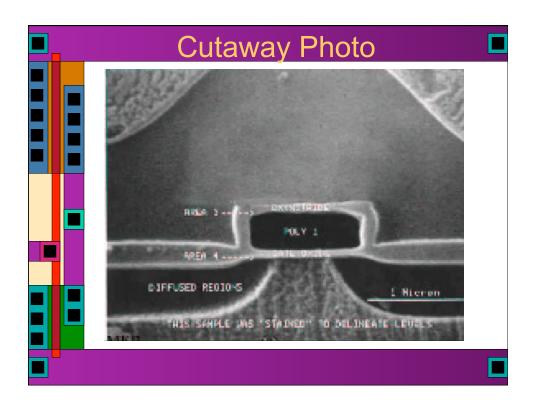

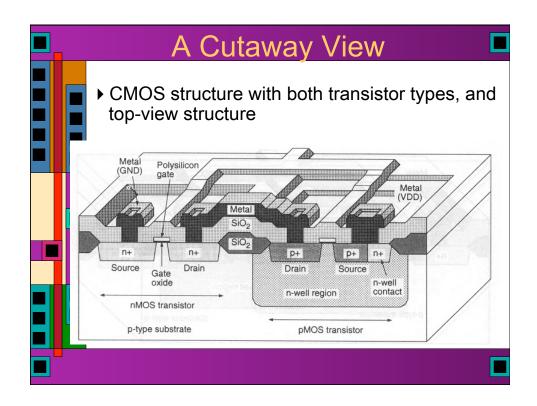

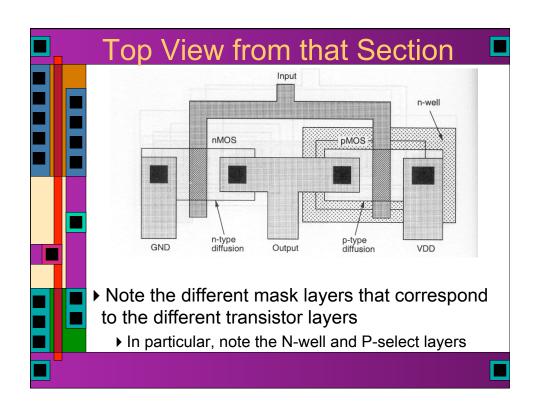

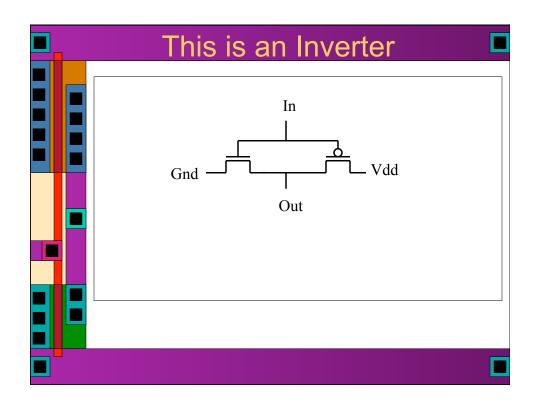

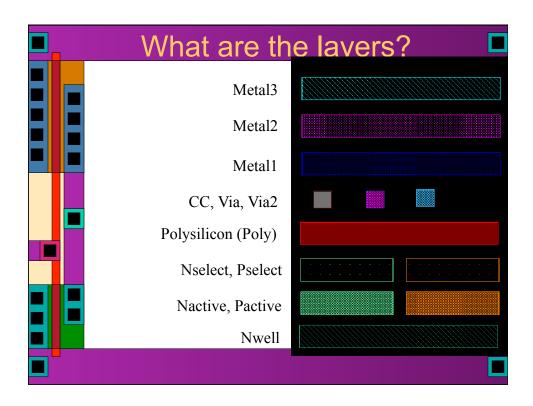

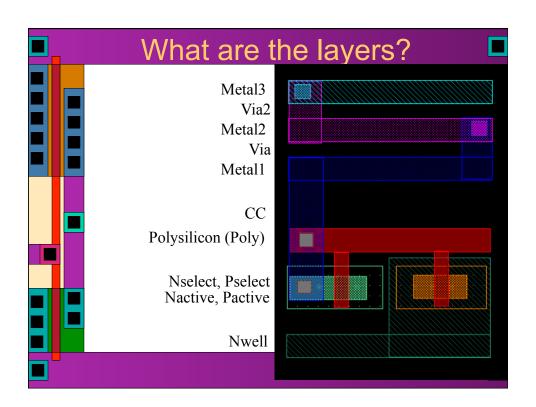

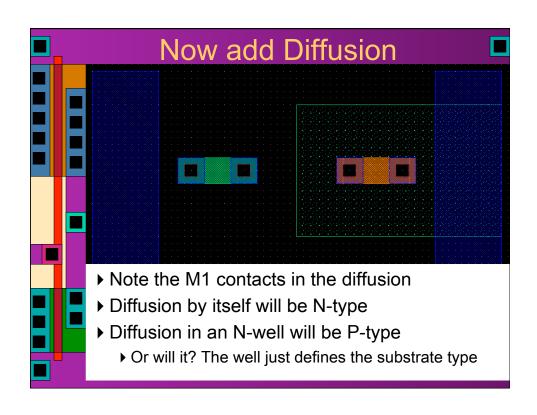

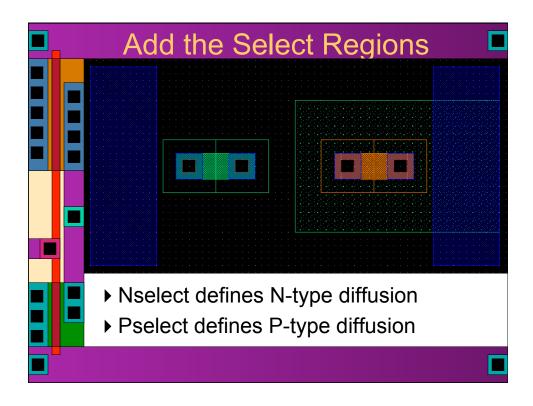

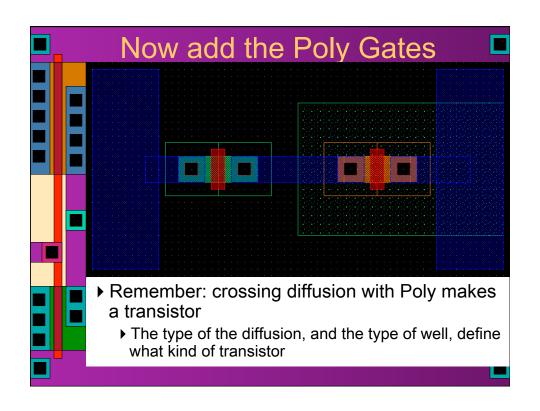

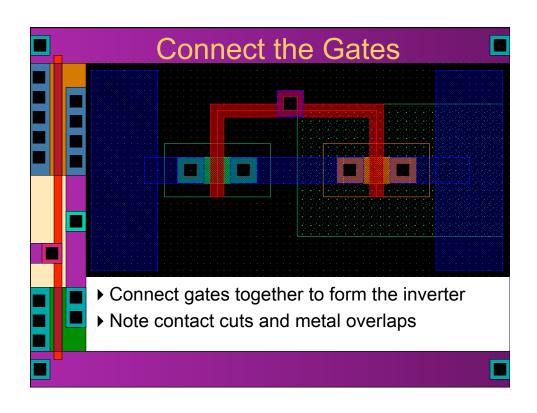

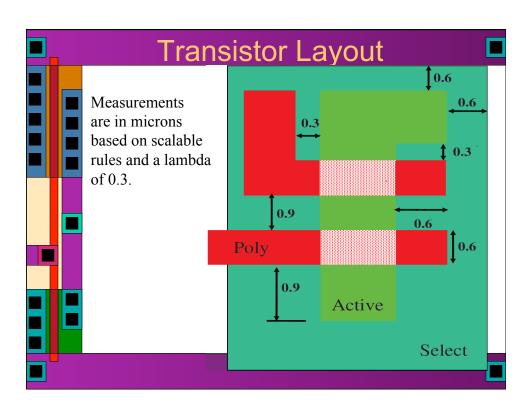

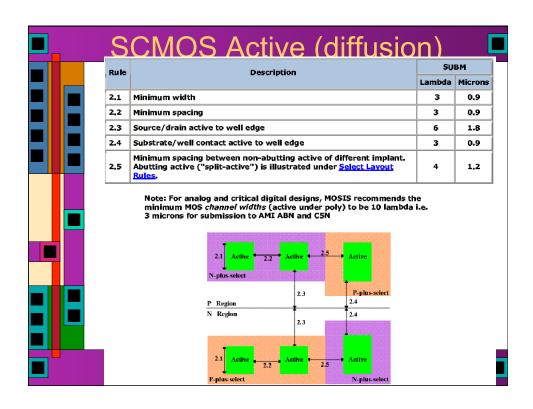

- ▶ Where poly crosses active = transistor

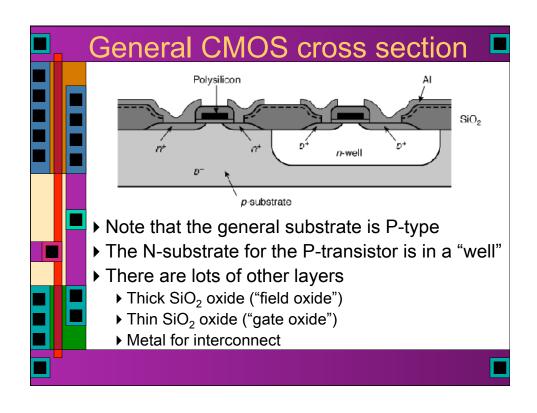

- ► For N-type, nactive over the substrate (p substrate)

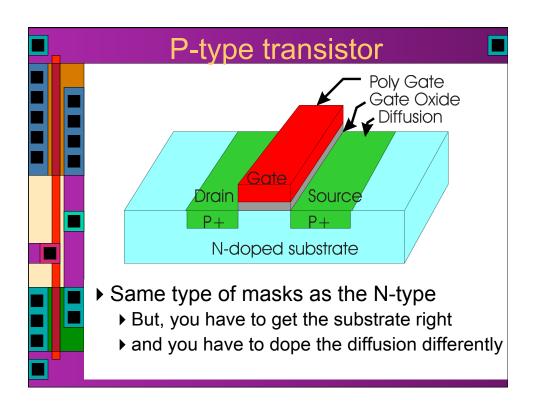

- ▶ For P-type, pactive inside an Nwell

- ▶ There's really only one "active" mask

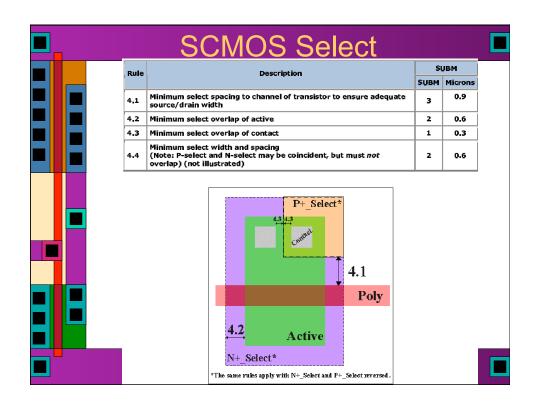

- nselect and pselect layers define active types

- ▶ Our setup has separate nactive and pactive colors to help keep things straight.

### **Layout Basics**

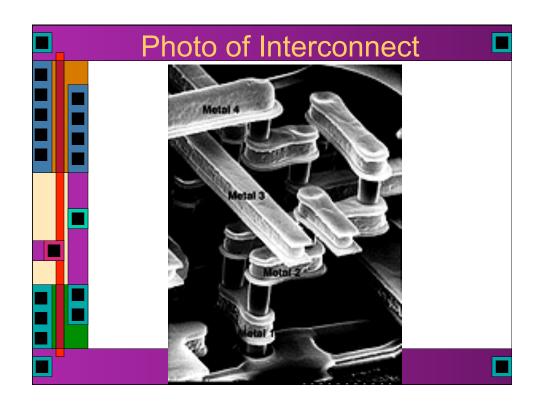

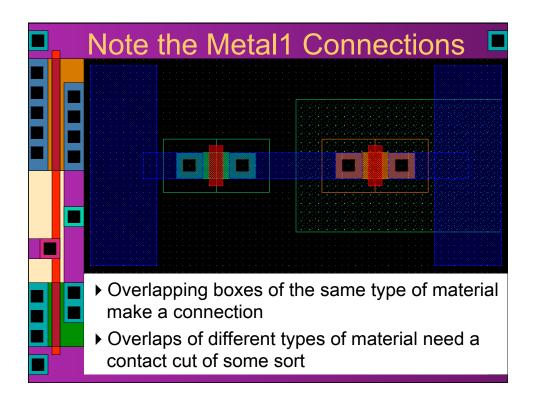

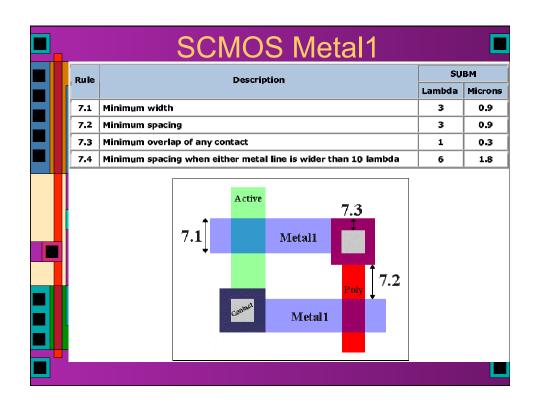

- ▶ Diffusion, Poly, and metal all conduct

- ▶ But resistances are very different

- ▶ Diffusion is worst, poly isn't too bad, metal is by far the best

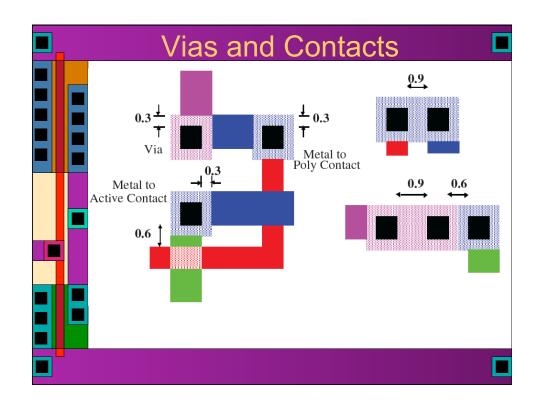

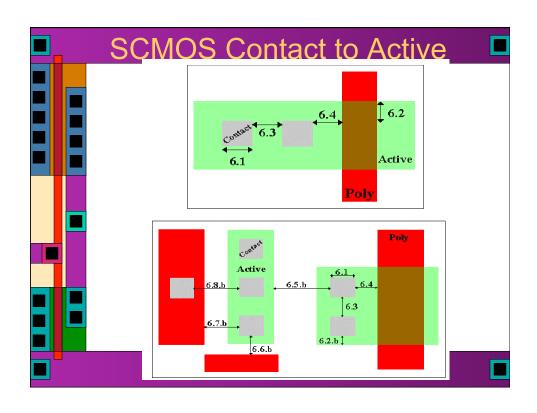

- Contact cuts are needed to connect between layers

- ▶ Make sure to use the right type of contact!

- ► CC for poly-M1, nactive-M1, pactive-M1

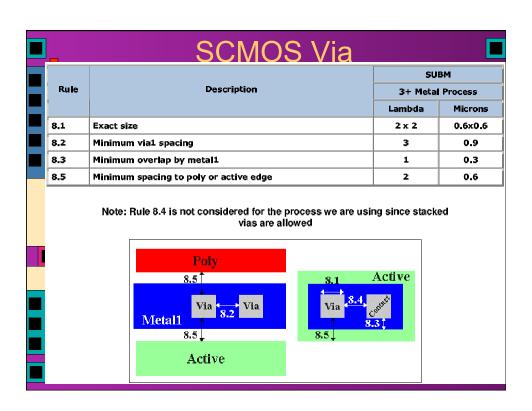

- ▶ Via1 for M1-M2

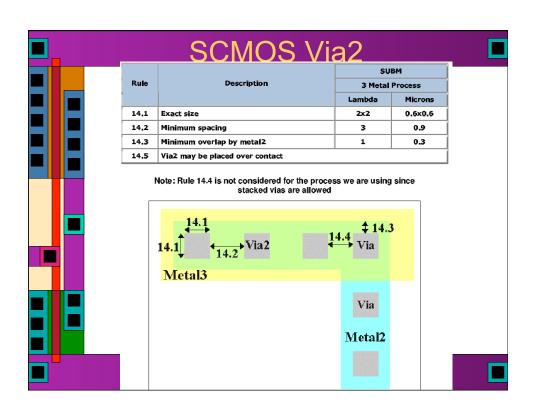

- Via2 for M2-M3

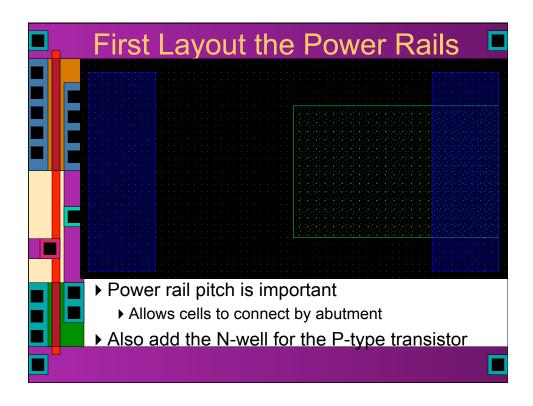

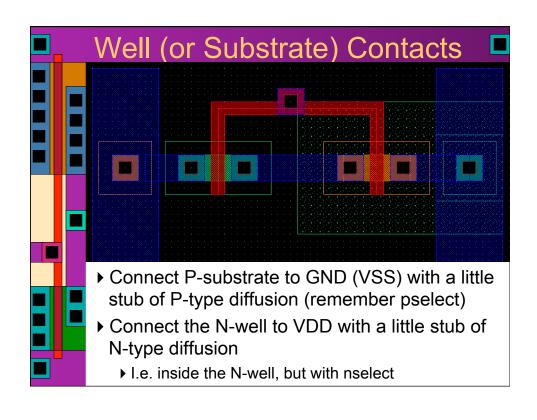

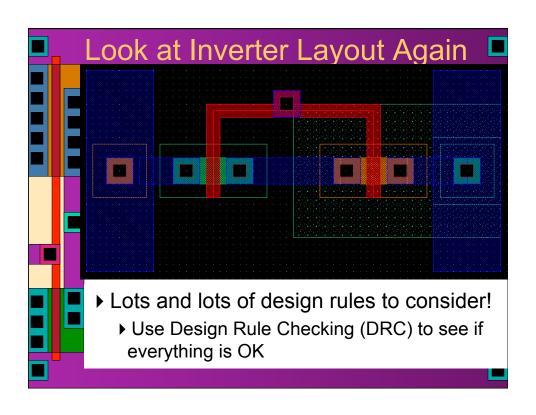

# Layout Subtlety ➤ We currently think of transistors as three-terminal devices ➤ Gate, Source, Drain ➤ They're really four-terminal devices ➤ There's also a connection to the substrate ➤ It's important to tie the substrate to a specific voltage ➤ GND for the P-substrate ➤ VDD for the N-well ➤ Make sure PN-diodes from active to substrate and well are reverse-biased...

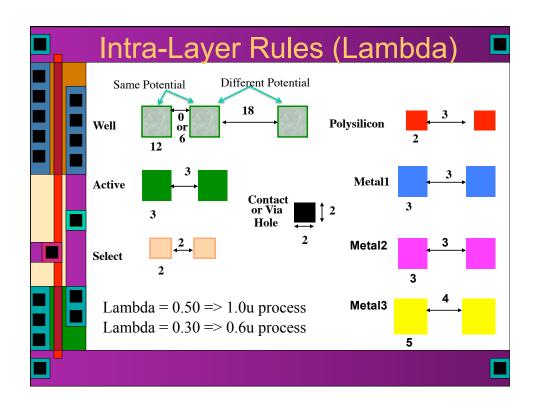

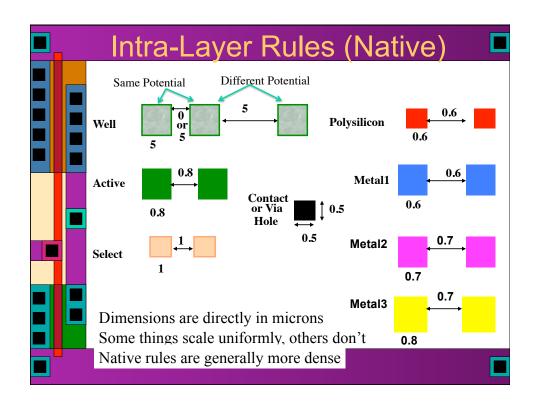

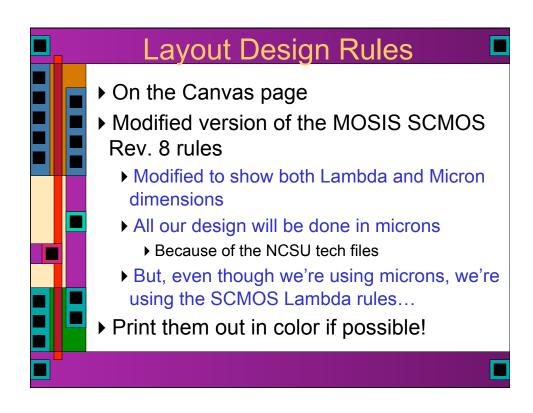

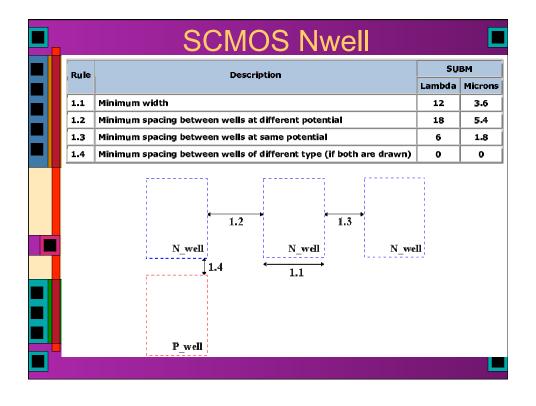

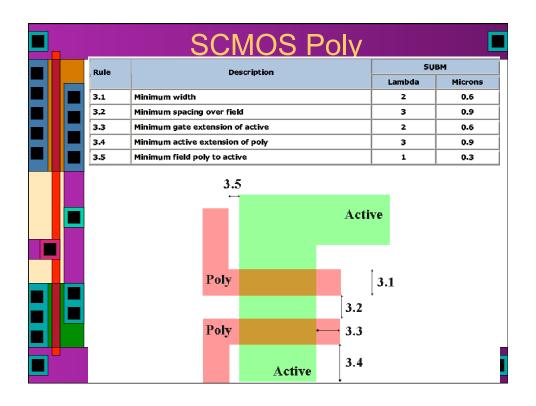

# Layout Design Rules Define the allowed geometry of the different layers Guidelines for making safe process masks Rules about the allowed sizes and shapes of a particular layer Rules about how different layers interact Dimensions listed in one of two ways Absolute dimensions (e.g. microns or nm) Scalable dimensions in abstract units Usually called "lambda" Design in lambda units, then scale lambda for a particular process

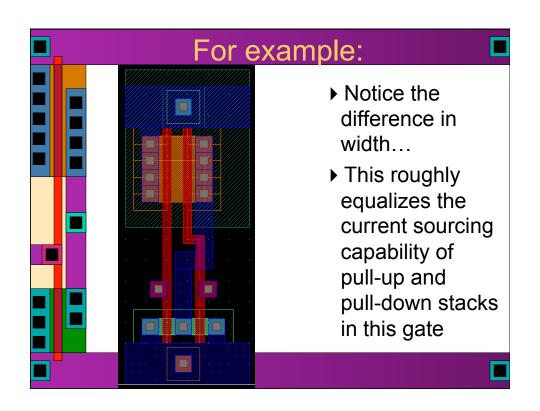

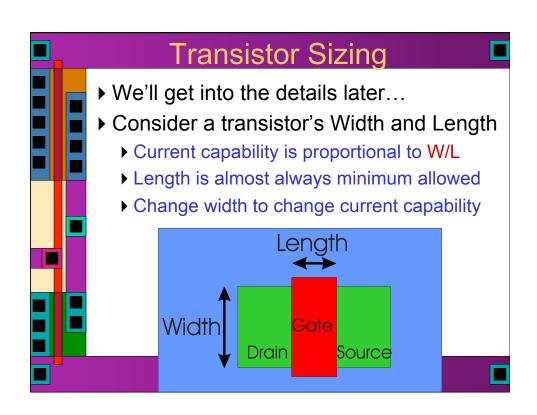

# Sizing Rule of Thumb

- ▶ Also, P-type is about twice as bad as N-type

- ▶ Has to do with hole mobility vs. electron mobility

- ➤ So, make P-types twice as wide as N-types to start with

- ▶ Unit size for transistors this semester

- ▶ N-type 1.5µ (contact pitch is 1.2µ)

- ▶ P-type 3µ

### Sizing Rule of Thumb

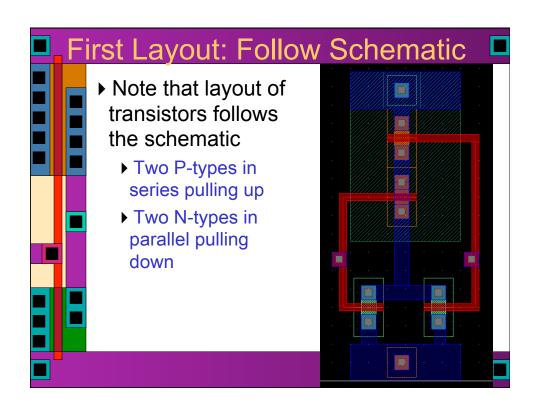

- ▶ Now multiply each width by n for a series stack of n transistors.

- ▶ Stack of 2 in series, each transistor should be 2x unit size

- ▶ Stack of 3 in series, each transistor should be 3x unit size

- ▶ This is because series connections are like increasing the L of the device...

- ▶ Current is proportional to W/L